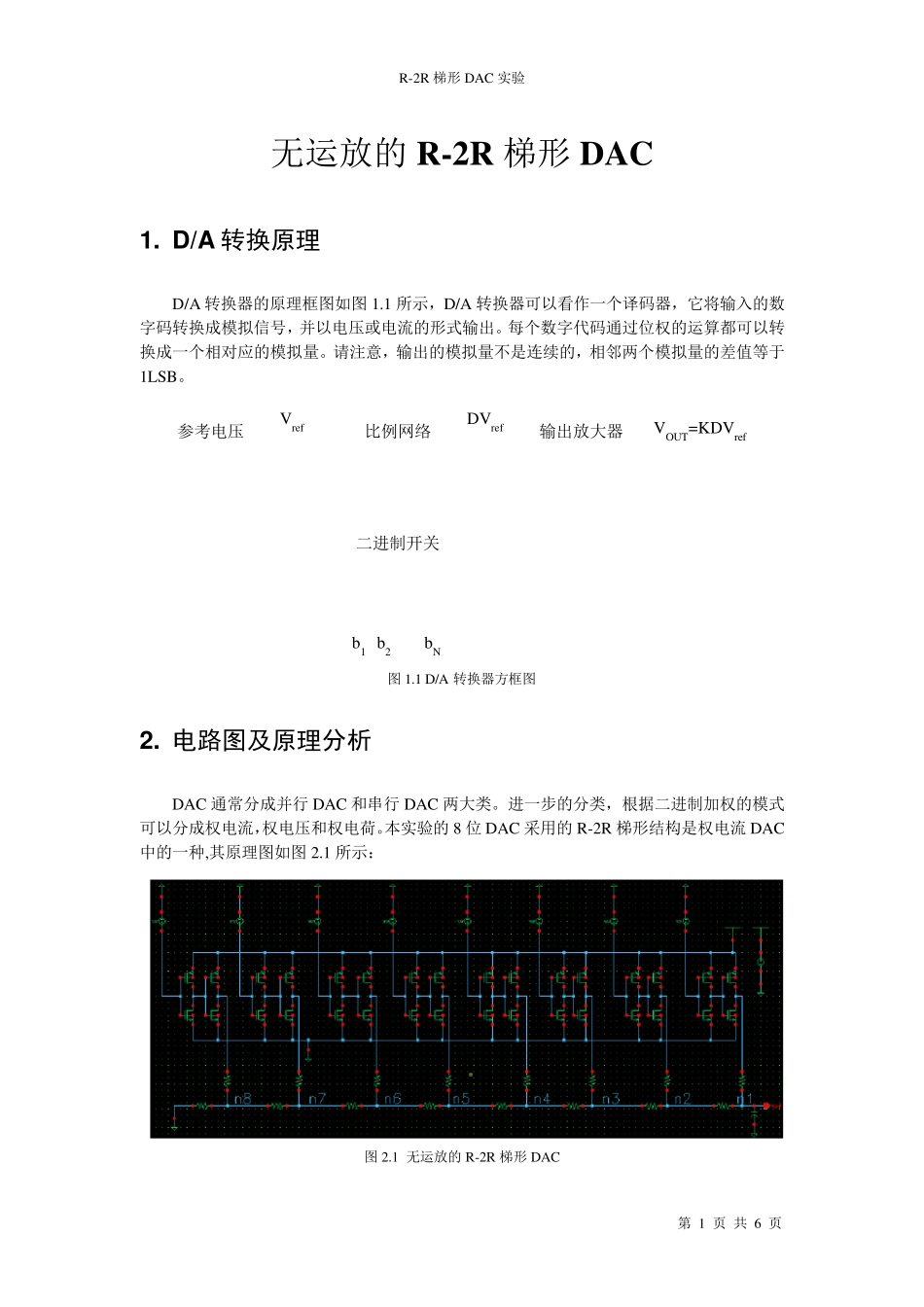

西安交通大学国家集成电路人才培养基地 第 I 页 共 6 页 国 家 集 成 电 路 人 才 培 养 基 地 培 训 资 料 (9) R -2R 梯形 D A C 设计 2006-X -X X 西安交通大学国家集成电路人才培养基地 第 II 页 共 6 页 R-2R 梯形DAC 实验 第 1 页 共 6 页 无运放的R -2R 梯形D A C 1. D /A 转换原理 D/A 转换器的原理框图如图1.1 所示,D/A 转换器可以看作一个译码器,它将输入的数字码转换成模拟信号,并以电压或电流的形式输出。每个数字代码通过位权的运算都可以转换成一个相对应的模拟量。请注意,输出的模拟量不是连续的,相邻两个模拟量的差值等于1LSB。 2. 电路图及原理分析 DAC 通常分成并行 DAC 和串行 DAC 两大类。进一步的分类,根据二进制加权的模式可以分成权电流,权电压和权电荷。本实验的8 位 DAC 采用的R-2R 梯形结构是权电流DAC中的一种,其原理图如图2.1 所示: 图2.1 无运放的R-2R 梯形DAC 参考电压 比例网络 输出放大器 二进制开关 Vref DVref b1 b2 bN VOUT=KDVref 图1.1 D/A 转换器方框图 西安交通大学国家集成电路人才培养基地 第 2 页 共 6 页 其中每一位的结构如图2.2 所示: 图2.1 中的VDD 取1.8 伏,电阻网络的特点是,整个网络只有R 和2R 两种阻值的电阻,其中R=2K,且从任意一个2K 电阻的左端向左看,所看到的电阻均等于2K。假定 bi=1,其余的所有数字代码均为 0,此时电路结构如图2.3 所示: 运用戴维南等效,可以得到bi 对 Vou t 的贡献为 VDD/2i,具体过程如图2.4 所示: 图2.2(a) 最低位的结构 图2.2(b) 第i 位的结构 图2.3 bi 位输入 1 其余位输入 0 等效电路 R-2R 梯形DAC 实验 第 3 页 共 6 页 运用线性叠加原理,叠加所有输入码对Vou t 的贡献得: NiiDDiou tVbV12 (2.1) 3 . 仿真结果分析 将VDD 设为1.8V,然后再给每个输入端加上脉冲源,最低位的周期为T,次低位周期为2T,周期成倍增大,如此设置好所有脉冲源,以使DAC 依次遍历所有可能的编码。从 00000000(=0V)以1.8/256 或 7.031mV(1LSB)为增量上升到 11111111(=1.8V-1LSB),仿真结果如图 3.1 所示: 图 2.4 bi 位输入1 输出等效 西安交通大学国家集成电路人才培养基地 第 4 页 共 6 页 放大显示倍数,图3.1 中的波形细节如图3.2 所示: 从图3.2 我们可以看到,正如我们所预料的每个“台阶”的高度(1LSB)为 7mV 左右。 图3.1 8 位 DAC 仿真结果 图3.2 放大显示输出波形