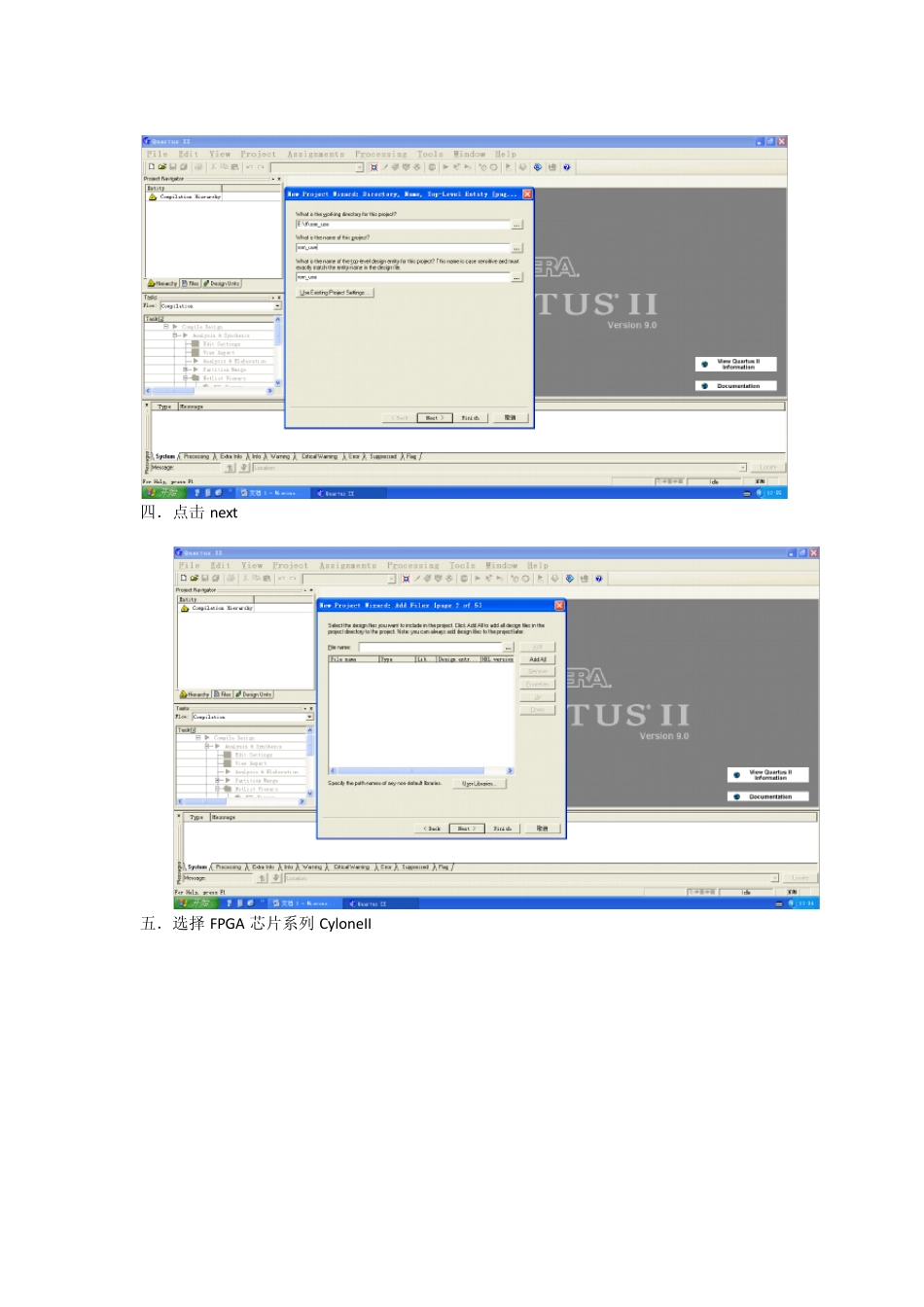

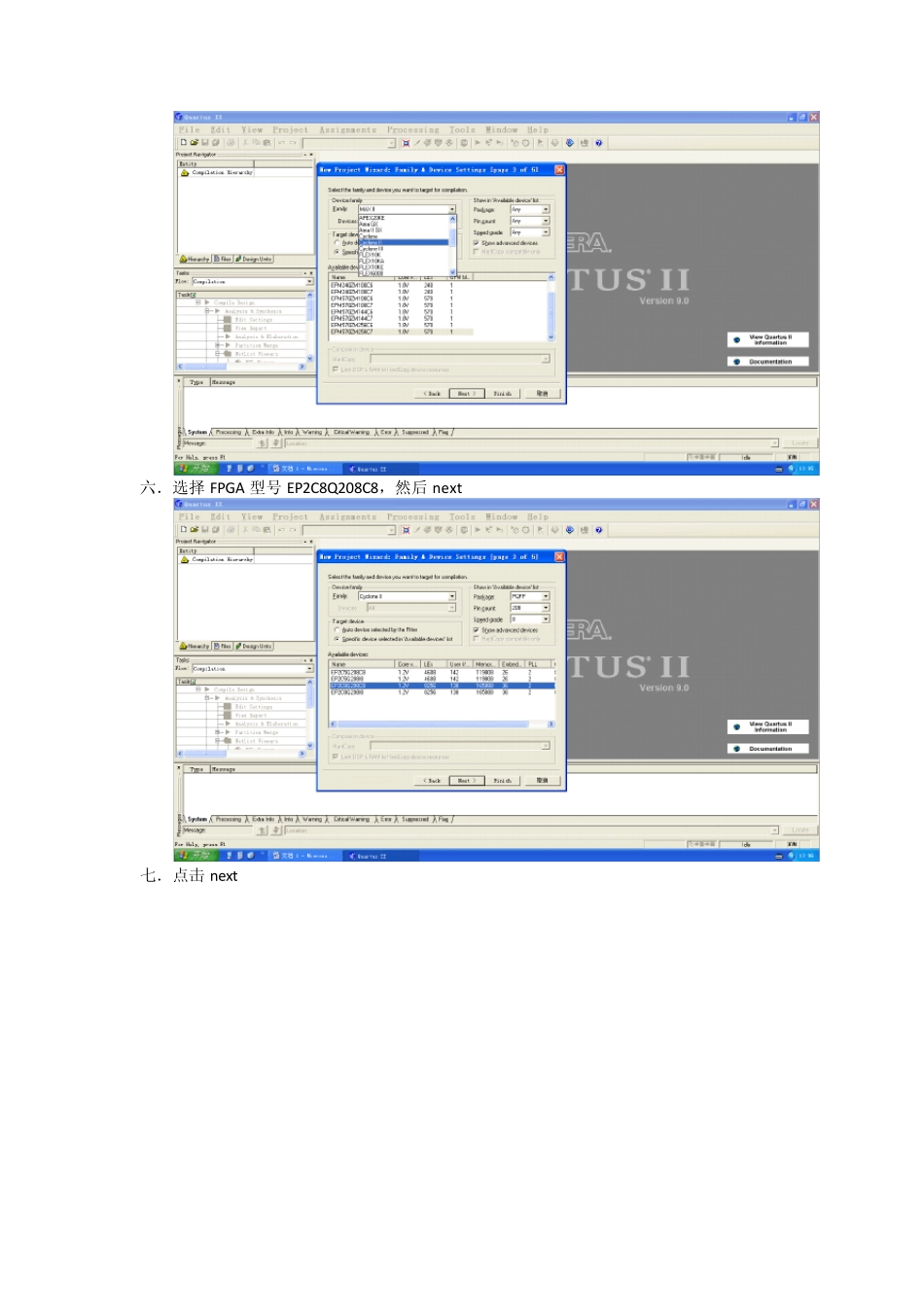

IP 核调用步骤 一.打开QUARTUSII 软件 二.新建工程 三.填写工程路径,工程名和实体名。(工程路径不要有中文,工程名和实体名相同),填写好后,点击 next. 四.点击next 五.选择 FPGA 芯片系列 CyloneII 六.选择FPGA 型号EP2C8Q208C8,然后next 七.点击 next 八.点击next 九.点击finish,新建工程完成。 十.选择工具“Assignments”的下拉菜单”Device…”选项,如下图: 十一.点击“Device and Pins Options..”如下图: 十二.选择未用管脚“u nu sed pins”将未用管脚设为“As inpu t tri-stated” 十三.再选择“configu ration”,将”Au to”换成“EPCS4”后,点击”确定“ 十四.点击“OK”,工程设置完成。 十五.新建 VHDL 程序,点击“OK“ 十六.编写程序 十七.程序编写完,保存 十八.新建ROM 初始化数据文件,点击“OK“ 十九.选择容量和位宽。在本例,容量为 64 个字节,位宽为 8bit。然后点“OK“ 二十.往里面填数据,在这里可以把我给的例程的数据直接拷进去,填完后保存。 二十一.新建 ROM 核,如下操作 二十二.点击next 二十三.先看上面有“AHDL”, ”VHDL,” “Verilog HDL”,在“VHDL”前面的圈里点击选中。 然后在路径后面给新建的ROM起一个名字:rom1,然后再在左边选中“ROM: 1-PORT”, 设置完后点next. 二十四.设置ROM 的位宽为8,容量为64,点击next. 二十五.点击“next”. 二十六. 点击“Browsr..”选择初始化数据文件的路径,初始化数据文件后缀为.mif。打开. 二十七.点击next 二十八.一直点next,直到如下图后,点finish,ROM 核创建完成。 二十九.编译一次 三十.编译成功后,选择“Assignment”菜单下的“Pins”,如下图 三十一.根据脚位表绑定管脚 三十二.绑完后,再编译一次。 三十三.编译成功后,下载程序 说明:程序下载方式,看拷个你们的培训一里面有一个“配套资料“文件夹下的,JTAG 下载方式。