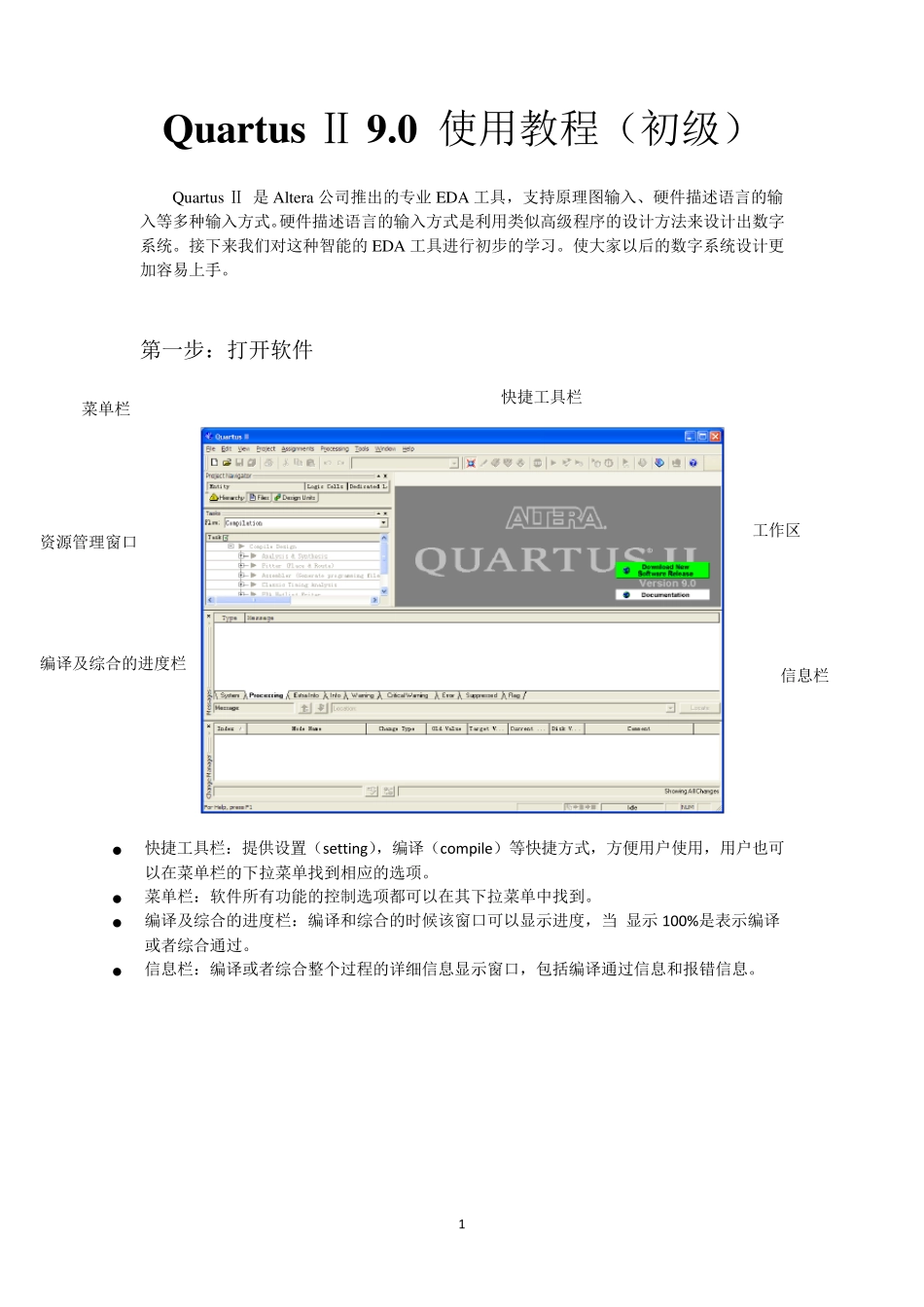

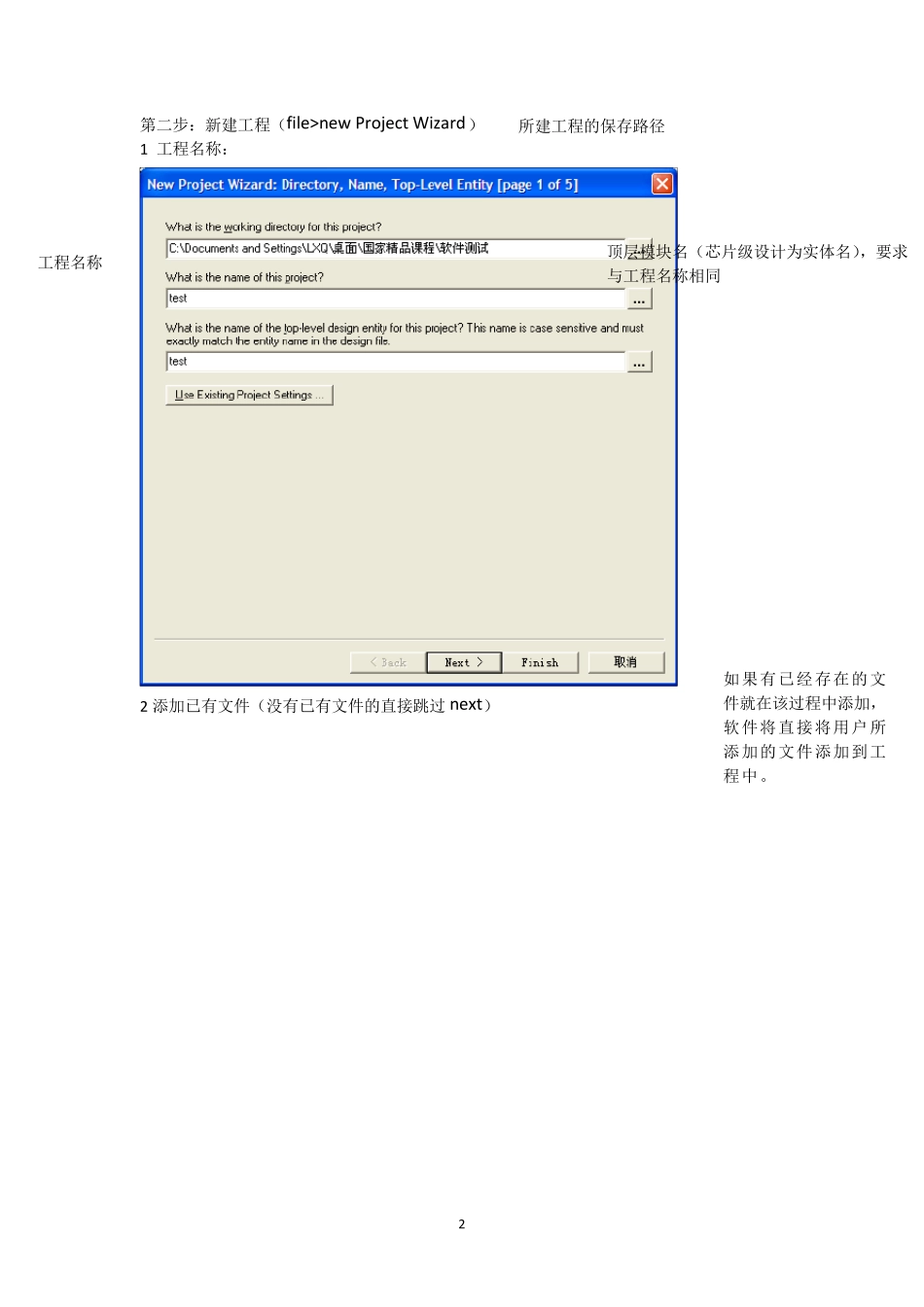

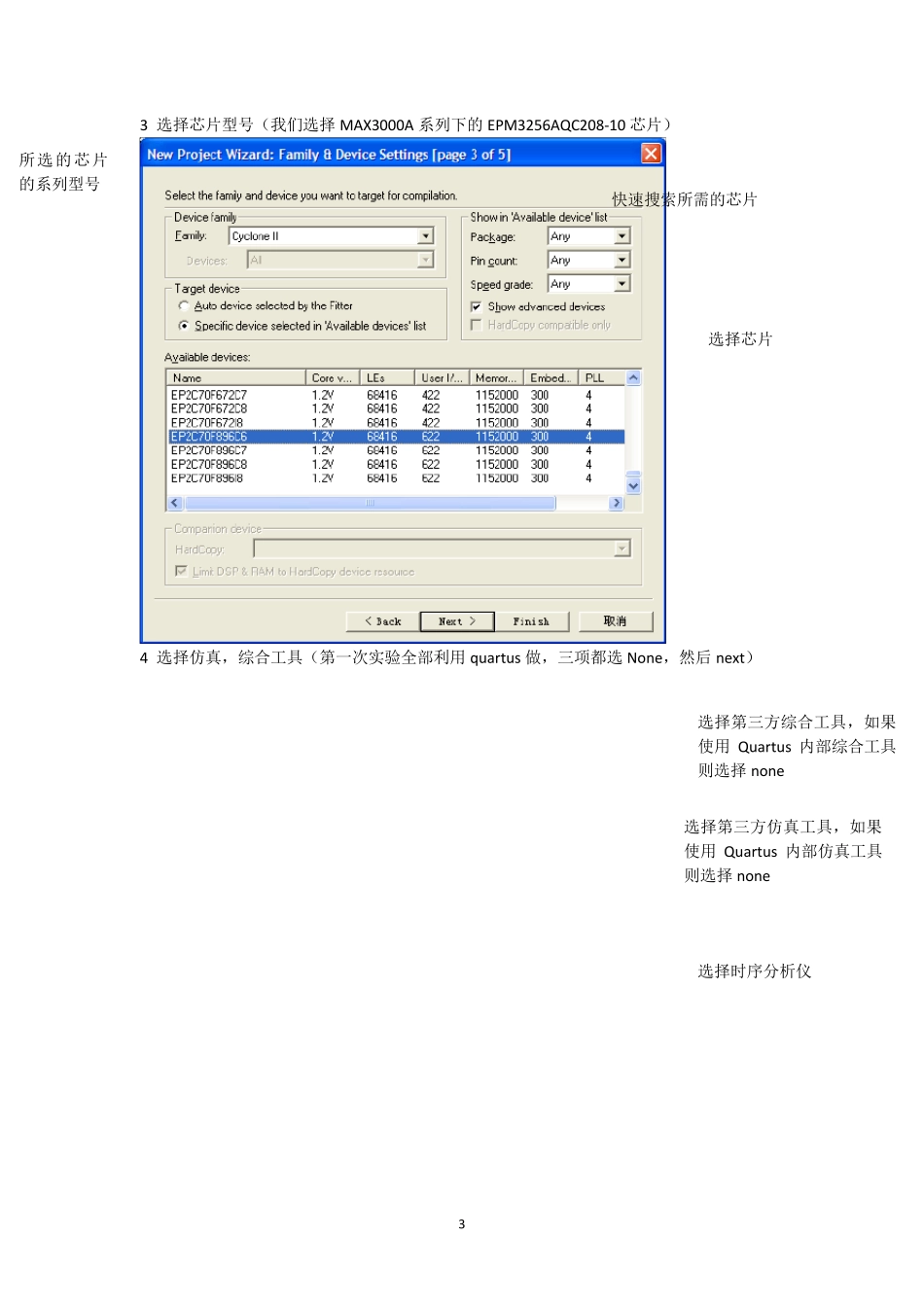

1 Qu artu s Ⅱ 9.0 使用教程(初级) Qu artu s Ⅱ 是 Altera 公司推出的专业 EDA 工具,支持原理图输入、硬件描述语言的输入等多种输入方式。硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。接下来我们对这种智能的 EDA 工具进行初步的学习。使大家以后的数字系统设计更加容易上手。 第一步:打开软件 快捷工具栏:提供设置(setting),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。 菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。 编译及综合的进度栏:编译和综合的时候该窗口可以显示进度,当 显示 100%是表示编译或者综合通过。 信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。 快捷工具栏 编译及综合的进度栏 信息栏 菜单栏 工作区 资源管理窗口 2 第二步:新建工程(file>new Project Wizard) 1 工程名称: 2 添加已有文件(没有已有文件的直接跳过next) 所建工程的保存路径 工程名称 顶层模块名(芯片级设计为实体名),要求与工程名称相同 如果有已经存在的文件就在该过程中添加,软件将直接将用户所添加的文件添加到工程中。 3 3 选择芯片型号(我们选择MAX3000A 系列下的EPM3256AQC208-10 芯片) 4 选择仿真,综合工具(第一次实验全部利用 quartus 做,三项都选None,然后 next) 所选的芯片的系列型号 快速搜索所需的芯片 选择芯片 选择第三方综合工具,如果使用 Quartus 内部综合工具则选择none 选择第三方仿真工具,如果使用 Quartus 内部仿真工具则选择none 选择时序分析仪 4 5 工程建立完成(点finish) 第三步:添加文件(file>new > VHDL file),新建完成之后要先保存。 工程建立完成,该窗口显示所建立工程所有的芯片,其他第三方 EDA 工具选择情况,以及模块名等等信息。 5 第四步:编写程序 3-8 译码器的VHDL 描述源文件如下: library ieee; use ieee.std_logic_1164.all; entity decoder3_8 is port( A:in std_logic_vector(2 downto 0); EN:in std_logic; Y:out std_logic_vector(7 downto 0)); end decoder3_8; architecture example_1 of decoder3_8 is signal sel:std_logic_vector(3 downto 0); begin sel<=A & EN; with sel select Y <= "11111110" whe...