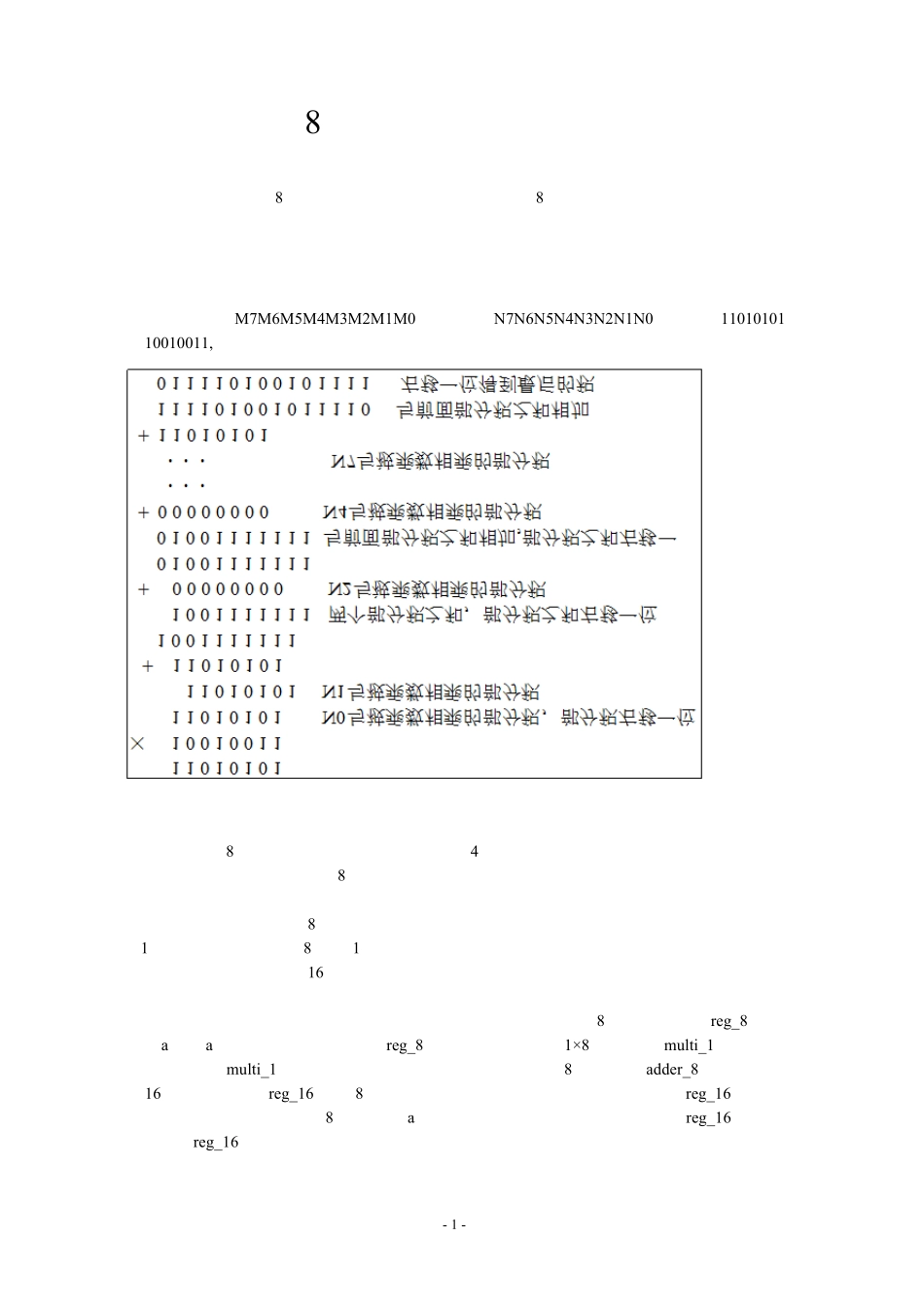

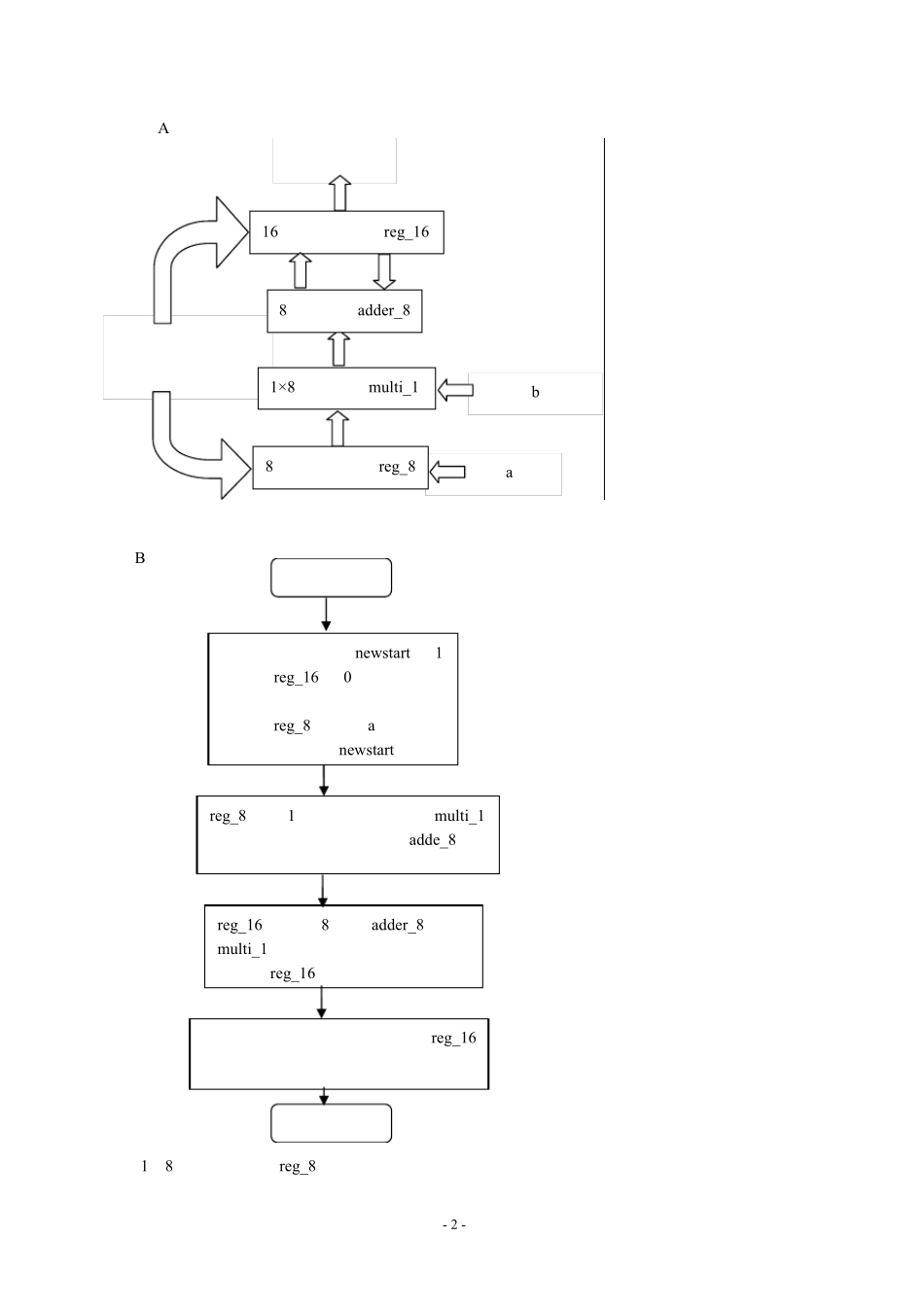

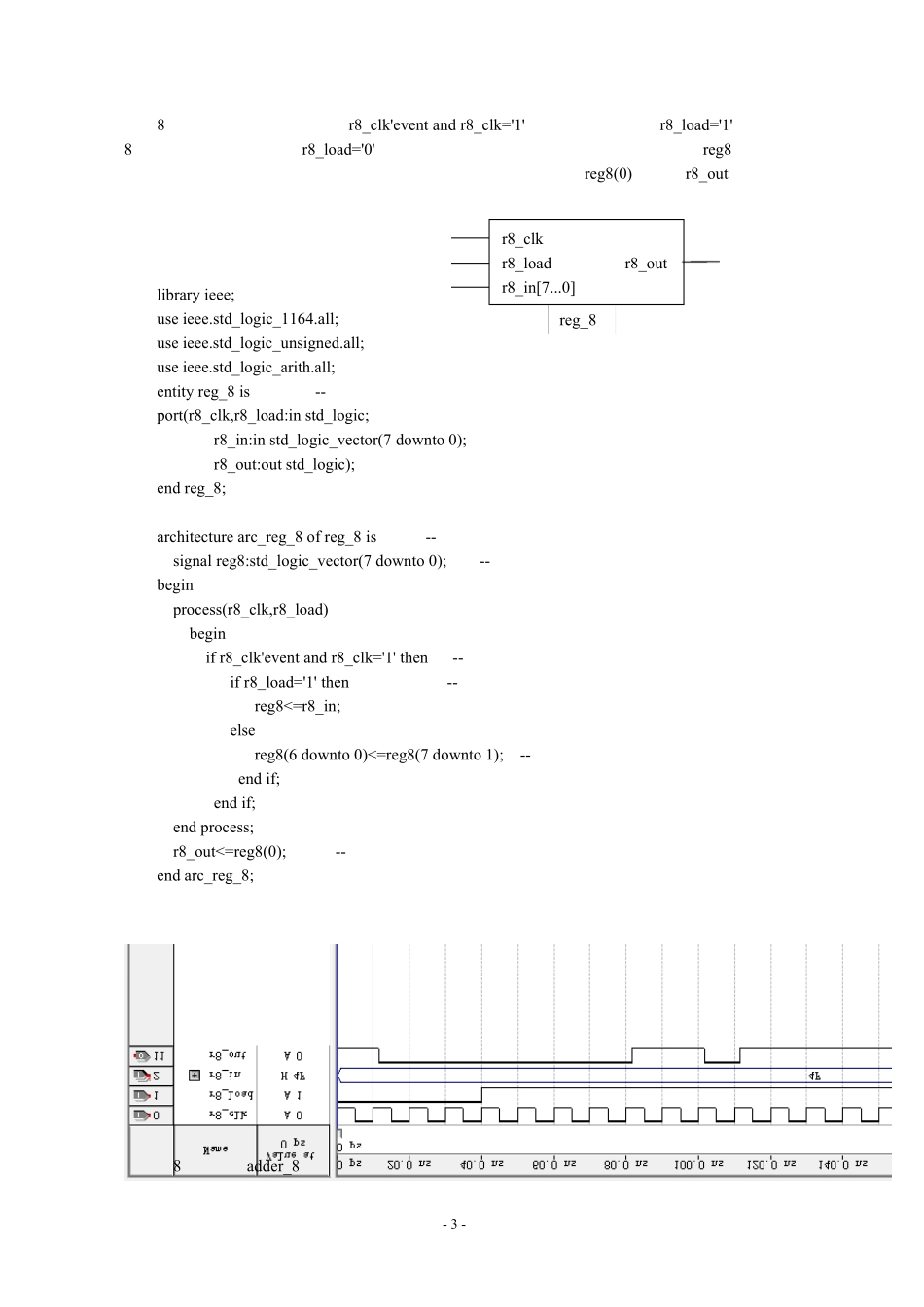

- 1 -8 位二进制乘法电路该乘法器是有由 8 位加法器构成的以时序方式设计的 8 位乘法器,采用逐项移位相加的方法来实现相乘。用乘数的各位数码,从低位开始依次与被乘数相乘,每相乘一次得到的积称为部分积,将第一次(由乘数最低位与被乘数相乘)得到的部分积右移一位并与第二次得到的部分积相加,将加得的和右移一位再与第三次得到的部分积相加,再将相加的结果右移一位与第四次得到的部分积相加。直到所有的部分积都被加过一次。例如:被乘数(M7M6M5M4M3M2M1M0)和乘数(N7N6N5N4N3N2N1N0)分别为 11010101和 10010011,其计算过程如下:下面分解 8 位乘法器的层次结构,分为以下 4 个模块:①右移寄存器模块:这是一个 8 位右移寄存器,可将乘法运算中的被乘数加载于其中,同时进行乘法运算的移位操作。②加法器模块:这是一个 8 位加法器,进行操作数的加法运算。③1 位乘法器模块:完成 8 位与 1 位的乘法运算。④锁存器模块:这是一个 16 位锁存器,同时也是一个右移寄存器,在时钟信号的控制下完成输入数值的锁存与移位。按照上述算法,可以得到下图所示之框图和简单流程图。图中 8 位移位寄存器 reg_8 存放乘数 a,从 a 的最低位开始,每次从 reg_8 中移出一位,送至 1×8 位乘法器 mu lti_1 中,同时将被乘数加至 mu lti_1 中,进行乘法运算,运算的结果再送至 8 位加法器 adder_8 中,同时取出 16 位移位寄存器 reg_16 的高 8 位与之进行相加,相加后结果即部分积存入 reg_16 中,进行移位后并保存。这样经过 8 次对乘数 a 的移位操作,所以的部分积已全加至 reg_16 中,此时锁存器 reg_16 存放的值即所要求的积。- 2 -(1)8 位移位寄存器 reg_8 的设计时钟、清零、移位控制信号,控制移位、清零或锁存乘数 a被乘数 b输出结果1×8 位乘法器 multi_18 位加法器 adder_88 位移位寄存器 reg_816 位移位寄存器 reg_16开始信号到来,置 newstart 为 1寄存器 reg_16 置 0时钟上升沿到来,寄存器 reg_8 置乘数 a时钟下降沿,置 newstart 为零开始reg_8 移出 1 位后与被乘数放入 multi_1中进行乘法运算,结果送至 adde_8reg_16 取出高 8 位送 adder_8 中,与multi_1 得到结果进行加法运算,结果送至 reg_16 右移后并进行锁存输出每一步的运算结果,即输出 reg_16的值,其中第八个值即为求得的积结束(A)电路框图(B)简单流程图- 3 ...