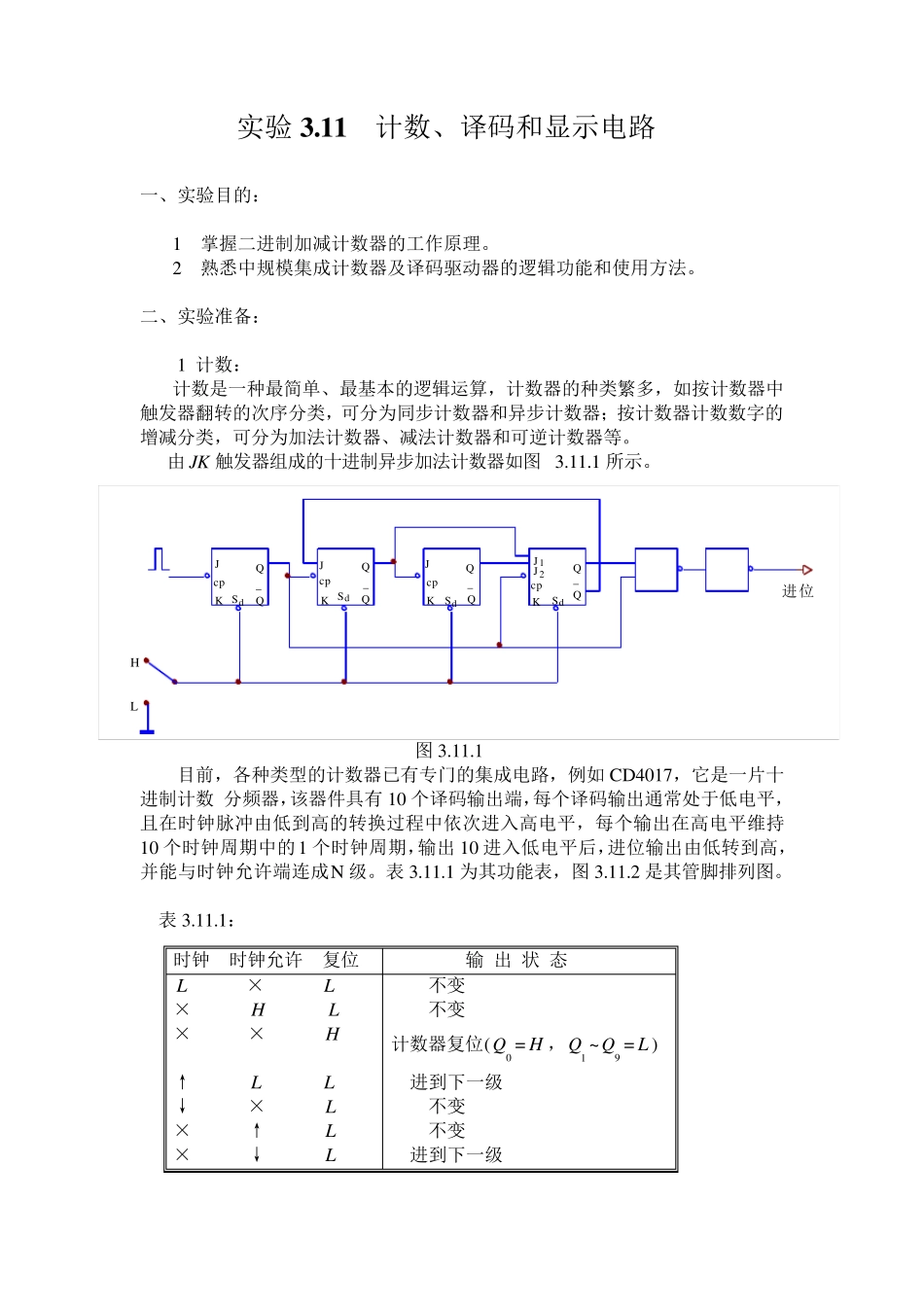

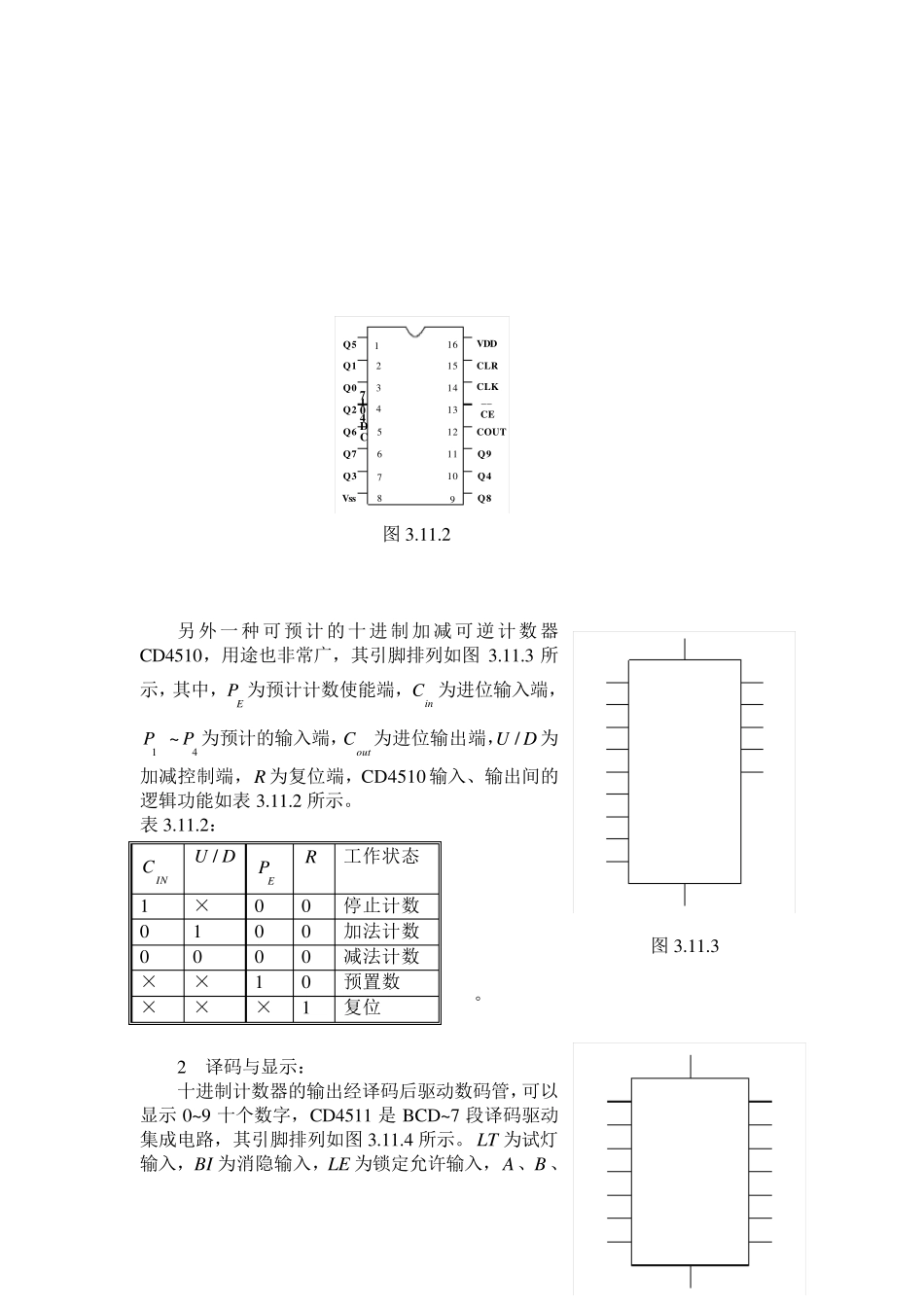

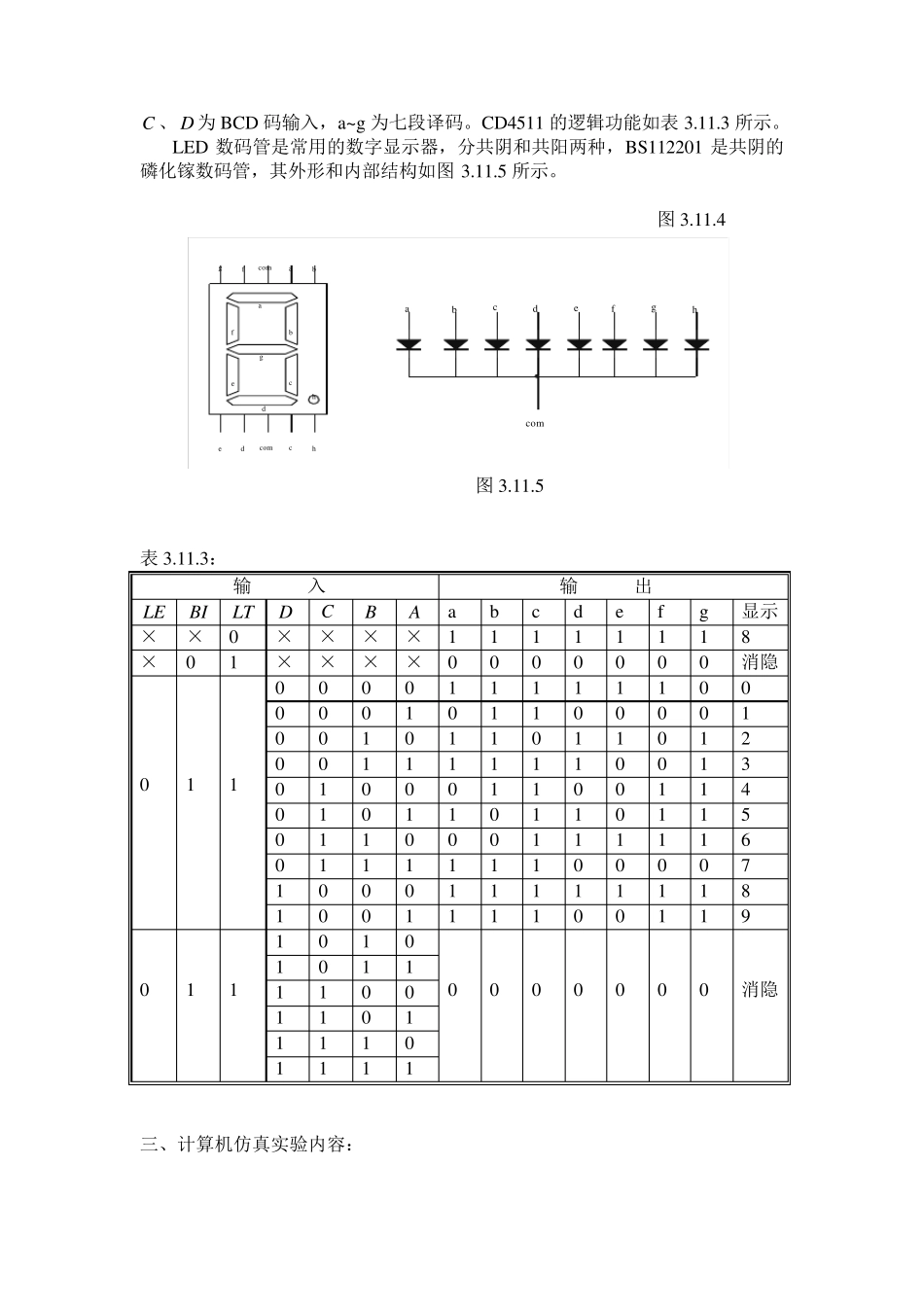

实验 3 .1 1 计数、译码和显示电路 一、实验目的: 1. 掌握二进制加减计数器的工作原理。 2. 熟悉中规模集成计数器及译码驱动器的逻辑功能和使用方法。 二、实验准备: 1.计数: 计数是一种最简单、最基本的逻辑运算,计数器的种类繁多,如按计数器中触发器翻转的次序分类,可分为同步计数器和异步计数器;按计数器计数数字的增减分类,可分为加法计数器、减法计数器和可逆计数器等。 由 JK 触发器组成的十进制异步加法计数器如图 3.11.1 所示。 图 3.11.1 目前,各种类型的计数器已有专门的集成电路,例如 CD4017,它是一片十进制计数/分频器,该器件具有 10 个译码输出端,每个译码输出通常处于低电平,且在时钟脉冲由低到高的转换过程中依次进入高电平,每个输出在高电平维持10 个时钟周期中的1 个时钟周期,输出 10 进入低电平后,进位输出由低转到高,并能与时钟允许端连成N 级。表3.11.1 为其功能表,图 3.11.2 是其管脚排列图。 表3.11.1: 时钟 时钟允许 复位 输 出 状 态 L × L × H L × × H ↑ L L ↓ × L × ↑ L × ↓ L 不变 不变 计数器复位(0Q = H ,1Q ~9Q = L ) 进到下一级 不变 不变 进到下一级 HLJJJJJKKKKcpcpcpcpQQQQQQQQSSSSdddd12____&&进位 图3.11.2 另外一种可预计的十进制加减可逆计数器CD4510,用途也非常广,其引脚排列如图3.11.3 所示,其中,EP 为预计计数使能端,inC 为进位输入端,1P ~4P 为预计的输入端,ou tC为进位输出端,U / D 为加减控制端,R 为复位端,CD4510 输入、输出间的逻辑功能如表3.11.2 所示。 表3.11.2: 图3.11.3 。 2. 译码与显示: 十进制计数器的输出经译码后驱动数码管,可以显示0~9 十个数字,CD4511 是BCD~7 段译码驱动集成电路,其引脚排列如图3.11.4 所示。LT 为试灯输入,BI 为消隐输入,LE 为锁定允许输入,A、B 、INC DU / EP R 工作状态 1 × 0 0 停止计数 0 1 0 0 加法计数 0 0 0 0 减法计数 × × 1 0 预置数 × × × 1 复位 12345678910111213141516PPPPPCCRU/DVVQQQQ12341234SSDDoutinCP_E12345678910111213141516ABCDLTBILE VVabcdefgSSDD__Q0Q1Q2Q3Q4Q5Q6Q7Q8Q9VDDVssCLKCLRCOUTCE__12345678910111213141516CD4017C 、D 为BCD 码输入,a~g 为七段译码。CD4511 的逻辑功能如表3.11.3 所示。 LED 数码管是常用的数字...