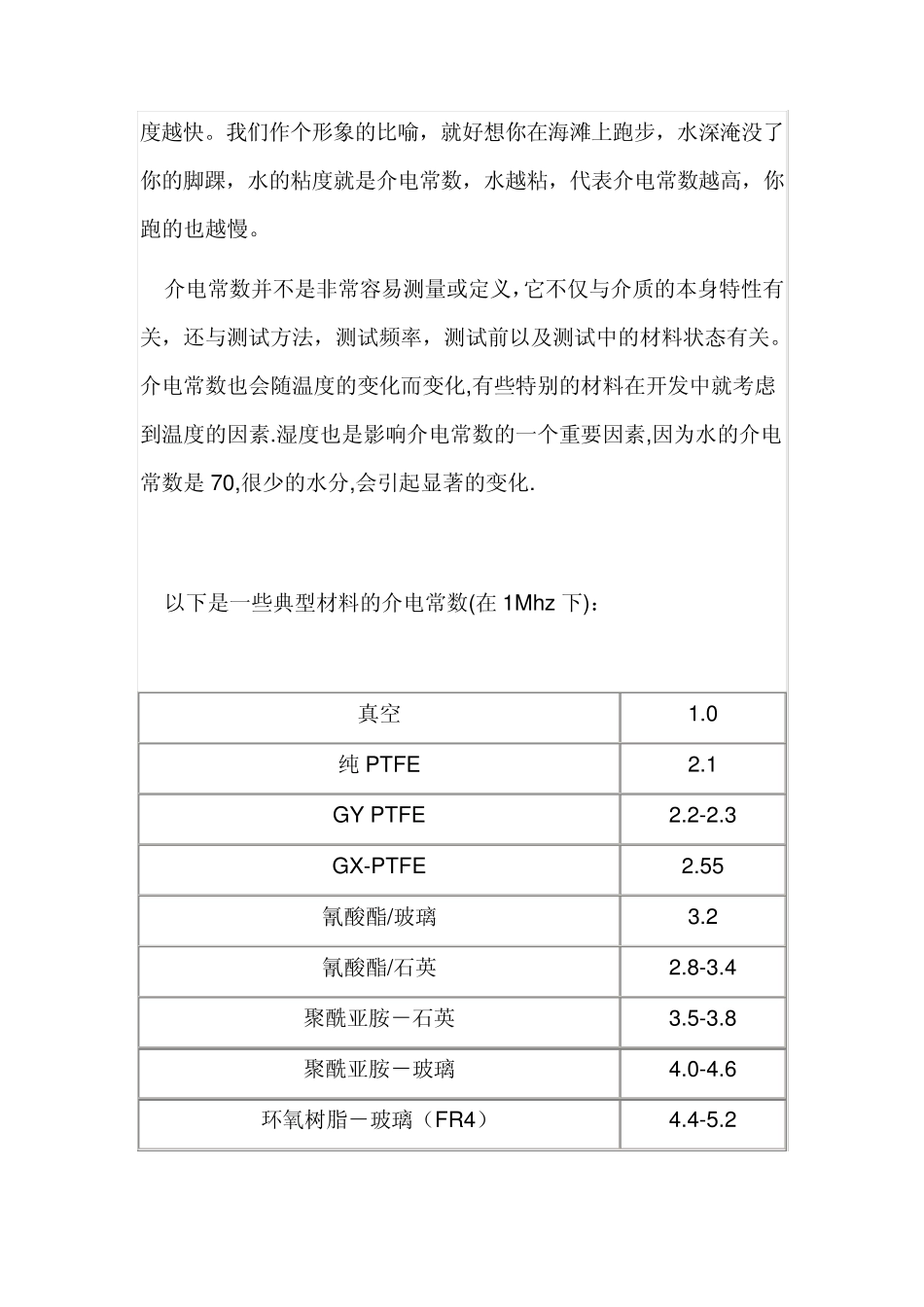

1、我们常用的 PCB 介质是 FR4 材料的,相对空气的介电常数是4.2-4.7。这个介电常数是会随温度变化的,在 0-70 度的温度范围内,其最大变化范围可以达到 20%。介电常数的变化会导致线路延时10%的变化,温度越高,延时越大。介电常数还会随信号频率变化,频率越高介电常数越小。100M 以下可以用 4.5 计算板间电容以及延时。 2、一般的 FR4 材料的 PCB 板中内层信号的传输速度为180ps/inch(1inch=1000mil=2.54cm)。表层一般要视情况而定,一般介于 140 与 170 之间。 3、实际的电容可以简单等效为 L、R、C 串联,电容有一个谐振点,在高频时(超过这个谐振点)会呈现感性,电容的容值和工艺不同则这个谐振点不同,而且不同厂家生产的也会有很大差异。这个谐振点主要取决于等效串联电感。现在的比如一个 100nF 的贴片电容等效串联电感大概在 0.5nH 左右,ESR(等效串联电阻)值为 0.1 欧,那么在24M 左右时滤波效果最好,对交流阻抗为 0.1 欧。而一个 1nF 的贴片电容等效电感也为 0.5nH(不同容值差异不太大),ESR 为 0.01 欧,会在 200M 左右有最好的滤波效果。为达好较好的滤波效果,我们使用不同容值的电容搭配组合。但是,由于等效串联电感与电容的作用,会在 24M 与 200M 之间有一个谐振点,在这个谐振点上有最大阻抗,比单个电容的阻抗还要大。这是我们不希望得到的结果。(在 24M到 200M 这一段,小电容呈容性,大电容已经呈感性。两个电容并联已经相当于LC 并联。两个电容的 ESR 值之和为这个 LC 回路的串阻。LC 并联的话如果串阻为 0,那么在谐振点上会有一个无穷大的阻抗,在这个点上有最差的滤波效果。这个串阻反倒会抑制这种并联谐振现象,从而降低 LC 谐振器在谐振点的阻抗)。为减轻这个影响,可以酌情使用 ESR 大些的电容。ESR 相当于谐振网络里的串阻,可以降低 Q 值,从而使频率特性平坦一些。增大 ESR 会使整体阻抗趋于一致。低于24M 的频段和高于200M 的频段上,阻抗会增加,而在 24M与 200M 频段内,阻抗会降低。所以也要综合考虑板子开关噪声的频带。国外的一些设计有的板子在大小电容并联的时候在小电容(680pF)上串几欧的电阻,很可能是出于这种考虑。(从上面的参数看,1nF 的电容 Q 值是 100nF 电容 Q 值的 10 倍。由于手头没有来自厂商的具体等效串感和 ESR 的值,所以上面例子的参数是根据以往看到的资料推测的。但是偏差应该不会太大。以往多处...