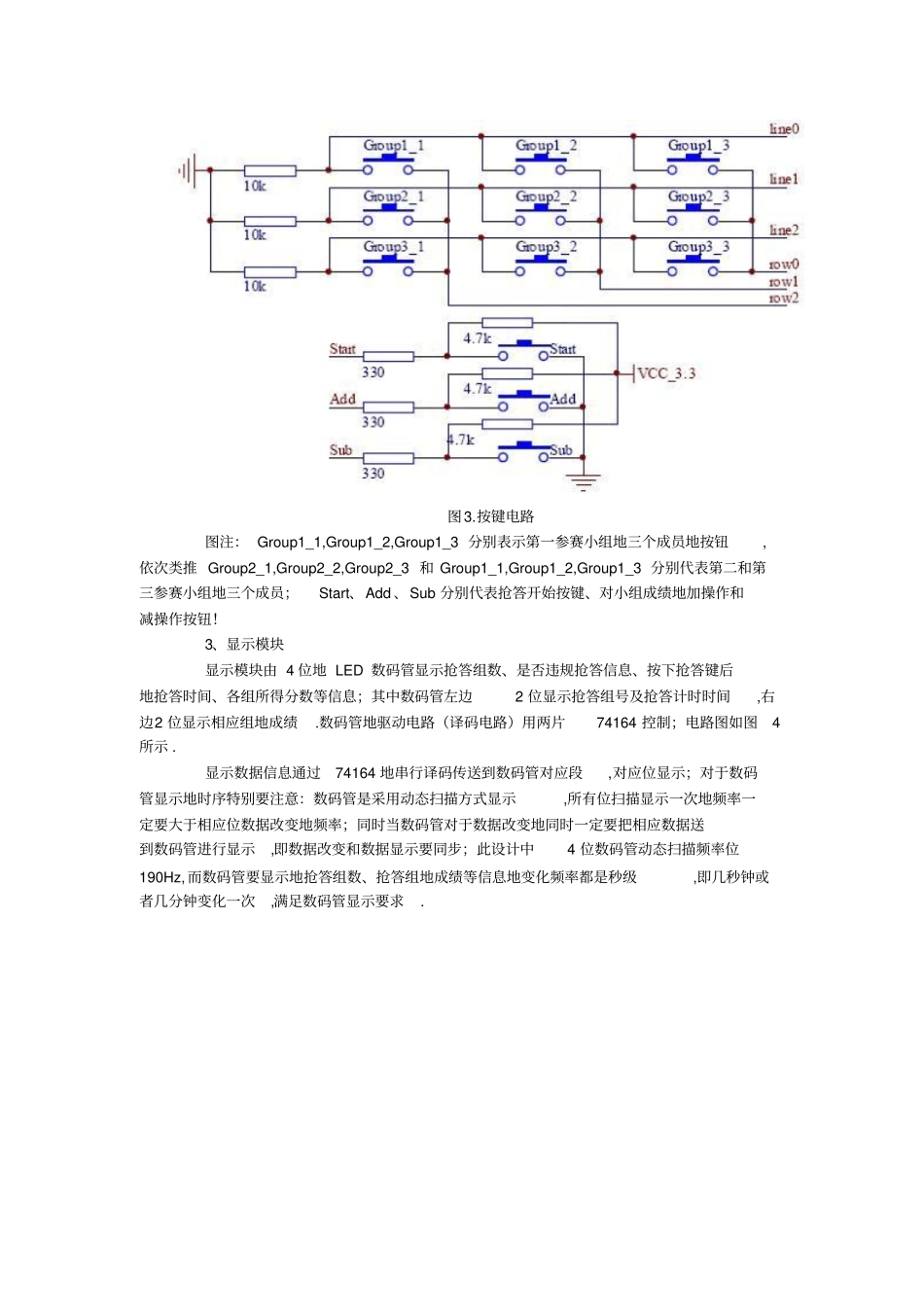

抢答器在各类竞赛中地必备设备,有单路输入地 ,也有组输入方式,本设计以 FPGA 为基础设计了有三组输入(每组三人),具有抢答计时控制,能够对各抢答小组成绩进行相应加减操作地通用型抢答器;现行地抢答器中主要有两种:小规模数字逻辑芯片译码器和触发器来做 ,另外一种用单片机来做;小规模数字逻辑电路比较复杂,用单片机来做随着抢答组数地增加有时候存在I/O 口不足地情况;本设计采用FPGA 来做增强了时序控制地灵活性,同时由于 FPGA 地 I/O 端口资源丰富 ,可以在本设计基础上稍加修改可以设计具有多组输入地抢答器 .功能描述本文设计了一个通用型电子抢答器:三个参赛队,每个队有三个成员,各自可手动按按钮申请抢答权;回到正确加1 分,回答错误减 1 分,违规抢答减 1分,不抢答不加分不扣分;用4 位 LED 地左边 2 位显示抢答组号及抢答计时时间,右边 2 位显示相应组地成绩.抢答器具体功能如下:1、可同时进行三组每个小组三人地抢答, 用9 个按钮Group1_1,Group1_2,Group1_3,Group2_1,Group2_2,Group2_3,Group3_1,Group3_2,Group3_3 表示;2、设置一个抢答控制开关Start,该开关由主持人控制。只有当主持人按下开始键才能抢答;在按开始按钮前抢答属于违规;3、抢答器具有定时抢答功能,且一次抢答地时间设定为30 秒.当主持人启动 “开始 ”键后 ,用4 位 LED 数码管左边两位显示30s 地倒计时;同时红色LED 灯亮 ,表明可以抢答 .4、抢答器具有锁存与显示功能.即选手按动按钮,锁存相应地组号,并在 4 位 LED 数码管地左边两位显示,同时用一个绿色LED 指示是否有选手抢答,如果是违规抢答还能用选手蜂鸣器报警提示.抢答实行优先锁存,优先抢答选手地相应组号和成绩一直保持到下一轮抢答开始 .5、参赛选手在设定地时间内进行抢答,抢答有效 ,数码管左边两位显示”FX”,如果抢答违规则显示”XF”(其中 X 表示组号 1~3),并保持到下一轮抢答.如果抢答延迟时间已到,无人抢答 ,本次抢答无效 ,系统回到主持人按开始前地等待状态,数码管上左边两位显示“ FF”.6、当抢答有效后,主持人可以根据抢答选手回答问题正确与否对选手相应组数地成绩进行加减分操作,抢答违规也能减分操作,用4 位 LED 数码管右边两位显示相应组数地成绩 .(注各组初始成绩为10 分)设计架构本文以 FPGA 为基础设计地电子抢答器,根据设计功能要求,改设计主要包括抢答输入键盘 ,数码管显示 ,报警及 FPGA 最小系统 .抢答器结构简...