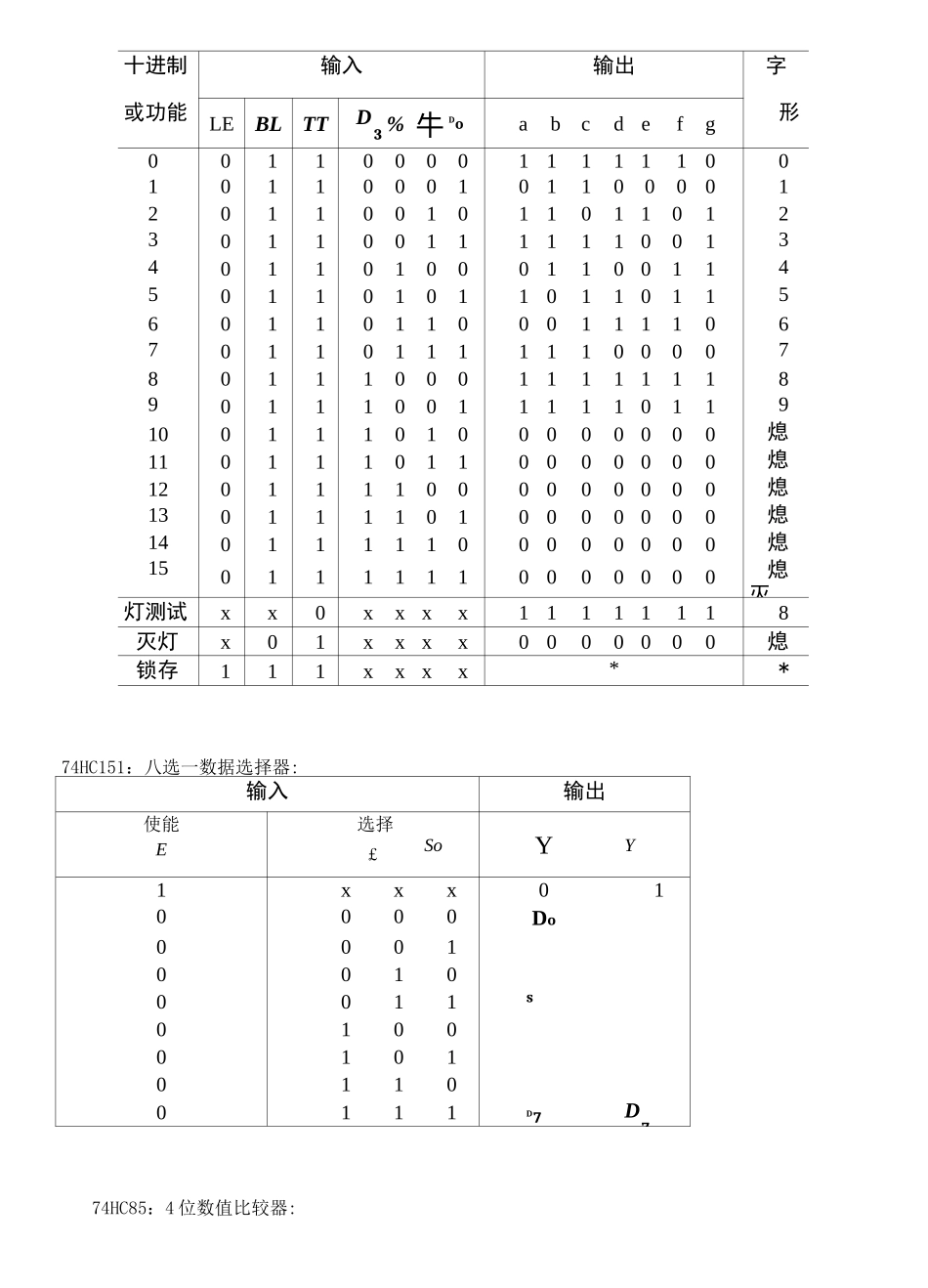

《VerilogHDL程序设计与仿真实验报告》1、实验名称:VerilogHDL程序设计与仿真实验2、实验设计要求以及内容:利用VerilogHDL语言和描述下列芯片的功能,编写激励测试程序并在Modelsim软件中仿真运行、记录相关波形。芯片包括:CD4532、74X138、74HC4511、74HC151、74HC85、74HC283、74HC194、74LVC161。3、实验软件:Modelsim软件。4、芯片功能与真值表:CD4532:8位优先编码器:输入输出EI767557272Y10Y2SYE00XXXXXXXX000001000000000000111XXXXXXX11110101XXXXXX110101001XXXXX1011010001XXXX10010100001XXX011101000001XX0101010000001X001101000000010001074X138:3线-8线译码器:输入输出214YT1Y2Y34□dYX1XXXX11111111XX1XXX111111111XXXXX11111111100000011111111000011011111110001011011111100011111011111001001111011110010111111011100110111111011001111111111074HC4511七段显示译码器:十进制或功能输入输出字形LEBLTTD3%牛Doabcdefg00110000111111001011000101100001201100101101101230110011111100134011010001100114501101011011011560110110001111067011011111100007801110001111111890111001111101191001110100000000熄灭1101110110000000熄灭1201111000000000熄灭1301111010000000熄灭1401111100000000熄灭1501111110000000熄灭灯测试xx0xxxx11111118灭灯x01xxxx0000000熄灭锁存111xxxx**74HC151:八选一数据选择器:输入输出使能E选择£SoYY1xxx010000Do000100100011s0100010101100111D7D774HC85:4位数值比较器:输入输出功能清零控制信号时钟串行输入并行输入On+1On+1On+1On+1xoxix2yCRss10CP右移D“左移D",%D11D1,D1.LHHHHHHxxLLLHLHHLHLHHxxffffxxxxLxHxxLxHxxxxxxxxxxxxxxxxxxxxxxxxxxD*D*D*D*10111213-LLLLOnOnOn0nx0X1x2x3LQnQnQnHQnQnQn74LVC161:4位二进制同步计数器:输入输出清零CR预支PE使能CEPCET预支数据输入DDDD2210Q3Q,Q1QO进位TCLxxxxxxxxLLLLLFUNCTIONTABLECOMPARINGINPUTSCASCADINGINPUTSOITPVTSA3nE3A2,B2ALE]Afl,EdIA>B1AB3XXXXXX21LLA3B2XXXXXHLLA3=B3A2^B2XXXXXLHLA:.:=B;A2=B2AI>B1XXXXHLLA3=B3A2=B:AJctivcHIGHj仪HHpLf*■(9+IQ■19)4.foractiveLO^r,csample■(cam-★$+$■⑵74HC194:4位双向移位寄存器:HHLHxLxxxD*3xD*2xD*ixD*0xDDDD3保持10##HHxLxxxxx保持LHHHHxxxx保持#5、实验具体设计:CD4532-8位优先编码器:模块设计代码:moduleCD4532(EI,I,Y,GS,EO);//8位优先编码器inputEI;input[7:0]I;outputreg[2:0]Y;outputregGS,EO;always@(EI,I)beginif(EI==0)beginY=3'd0;GS=0;EO=0;endelse//当EI=1时,实现优先编码器的功能beginGS=1;EO=0;//当编码器输入信号有效时,设定GS、EO的输出值if(I[7])Y=3'd7;else//根据I的高位情况对Y的输出进行控制if(I[6])Y=3'd6;elseif(I[5])Y=3'd5;elseif(I[4])Y=3'd4;elseif(I[3])Y=3'd3;elseif(I[2])Y=3'd2;elseif(I[1])Y=3'd1;elseif(I[0])Y=3'd0;elsebeginY=3'd0;GS=0;EO=1;end//当编码器输入信号无效时,设定GS、EO的输出值endendendmodule对应testbench设计代码:、timescalelns/lns//设定仿真时间间隔单位,之后的testbench中这句代码功能类似moduleCD4532_tb;reg[7:0]D_in;//设定testbench输入数据类型为reg型regEI_in;wire[2:0]Q_result;///设定testbench输出数据类型为wire型wireGS_result,EO_result;initialbeginEI_in=0;//初始化相关数据的值D_in=8'b0000_0001;#80EI_in=1;#80$stop();//上一个语句执行...