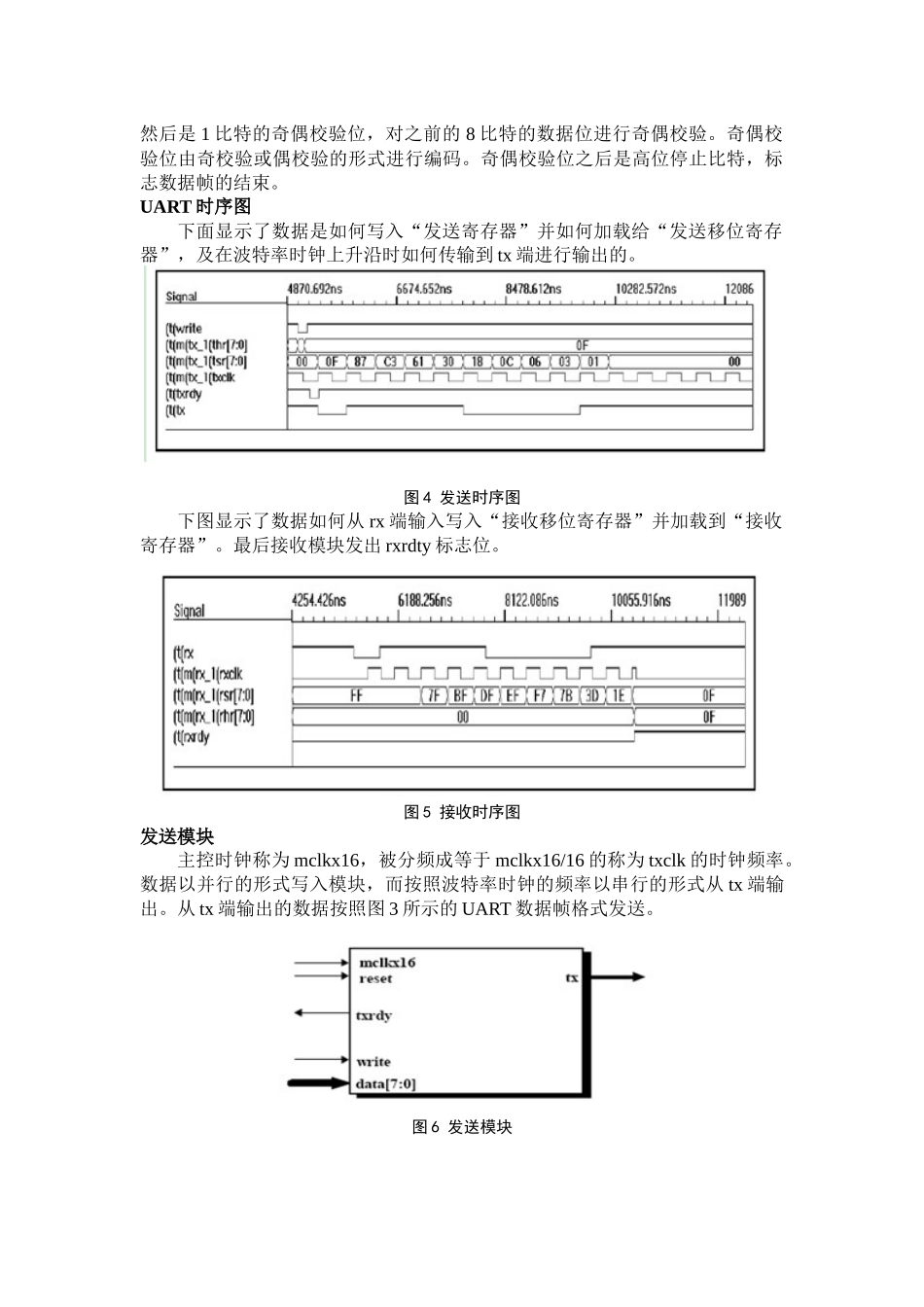

译文基于FPGA的串行控制器设计ThomasOelsnerQuickLogicEurope应用注释:QAN20简介目前设计开发和验证FPGA系统时,硬件描述语言HDL的使用变得越来越主流。采用行为级描述不仅提高了产品的设计效率,而且在设计验证中显示出其独特的优势。目前最流行的HDL语言是Verilog和VHDL语言。本文介绍了采用verilog语言对数字异步串行收发器进行设计和验证。UART通用异步串行收发器(UART)由二个独立的HDL模块组成。一个模块实现发射功能,而另一个模块则实现接收功能。发射和接收功能模块在顶层设计时组合到一起,这种接收和发射的组合是通信所必需的。数据写入发射器,从接收器读出,所有的数据是以二进制8字节的形式通过一个双向CPU接口。由地址映射的发射机和接收机通道可以很容易地建立接口。两个模块共用一个主控时钟,该时钟为mclkx16,在每个模块里,主控时钟mclkx16被分频成独立的波特率时钟。图1通用异步串行收发器通用异步串行收发器的特点是否具有全双工操作标准UART数据帧格式偶校验或奇校验模式奇偶错误校验帧错误校验溢出错误校验数据接收准备中断数据发送准备中断是是是是是是是是表UART功能概述UART的功能概况UART的基本功能概况见下图。左边为“发送寄存器”、“发送移位寄存器”以及“发送控制逻辑模块”,这些模块包含在发送模块”txmix”中。右边为“接收移位寄存器”、“接收寄存器”和“接收控制逻辑模块”,这些模块包含在发送模块”rxmix”中。这两个模块有单独的输入和输出的控制线路,只有双向的数据总线、主时钟和复位线是共享的。图2UART框图顶层UART系统的I/O功能描述符号类型描述mclkx16输入用于主控时钟波特率的生产。reset输入主复位输入信号。parityerr输出表明被检测的数据帧有无奇偶校验错误。校验编码可以基于偶数或奇数模式。framingerr输出表明从rx输入的数据串是否符合如图2所示的UART数据帧格式。overrun输出表明接收模块准备接收新数据是,模块中仍然有数据未读取。rxrdy输出表明接收模块已经接收新数据,并准备读取。txrdy输出表明数据已准备好加载到发送模块。read输入低电平有效的读选通信号,用于从接收模块中读取数据。write输入低电平有效的写选通信号,用于将数据写入发送模块。data[7:0]输入双向数据总线。数据通过该总线进行发送或接收。tx输出发送模块串行输出。复位或闲置时为高电平。rx输入接收模块串行输入。复位或闲置时为高电平。表2UART的I\O接口UART的标准数据格式图3UART数据帧格式图3为UART的串行数据格式,在串行数据帧中包含8位数据位以及编码比特的信息。在连续传输线路之间,传输线路处于高电平。传输从低位的起始比特开始,接下来的是8比特的数据信息,低位对于后边高位有重要的作用。然后是1比特的奇偶校验位,对之前的8比特的数据位进行奇偶校验。奇偶校验位由奇校验或偶校验的形式进行编码。奇偶校验位之后是高位停止比特,标志数据帧的结束。UART时序图下面显示了数据是如何写入“发送寄存器”并如何加载给“发送移位寄存器”,及在波特率时钟上升沿时如何传输到tx端进行输出的。图4发送时序图下图显示了数据如何从rx端输入写入“接收移位寄存器”并加载到“接收寄存器”。最后接收模块发出rxrdty标志位。图5接收时序图发送模块主控时钟称为mclkx16,被分频成等于mclkx16/16的称为txclk的时钟频率。数据以并行的形式写入模块,而按照波特率时钟的频率以串行的形式从tx端输出。从tx端输出的数据按照图3所示的UART数据帧格式发送。图6发送模块符号类型描述mclkx16输入用于生成主控时钟波特率。reset输入主复位输入信号write输入低电平有效的写选通信号,将数据写入发送模块。data[7:0]输入数据传输是通过数据总线写入发送模块。在写选通脉冲的上升沿,数据总线的内容锁定在一个内部的“发送寄存器”。tx输出串行数据输出。串行数据帧通过这个端口发送,当复位或闲置时,tx保持高电平。txrdy输出表明数据锁存到“发送寄存器”,同时加载到“发送移位寄存器”,“发送寄存器”准备好接收新数据。表2发送模块I\O接口功能符号类型内部标志或信号的描述thrreg[7:0]8位“发送寄存器”,用于锁存发送模块接收到的数据。tsrreg[7:0]...

VIP

VIP VIP

VIP VIP

VIP VIP

VIP VIP

VIP VIP

VIP VIP

VIP VIP

VIP VIP

VIP VIP

VIP