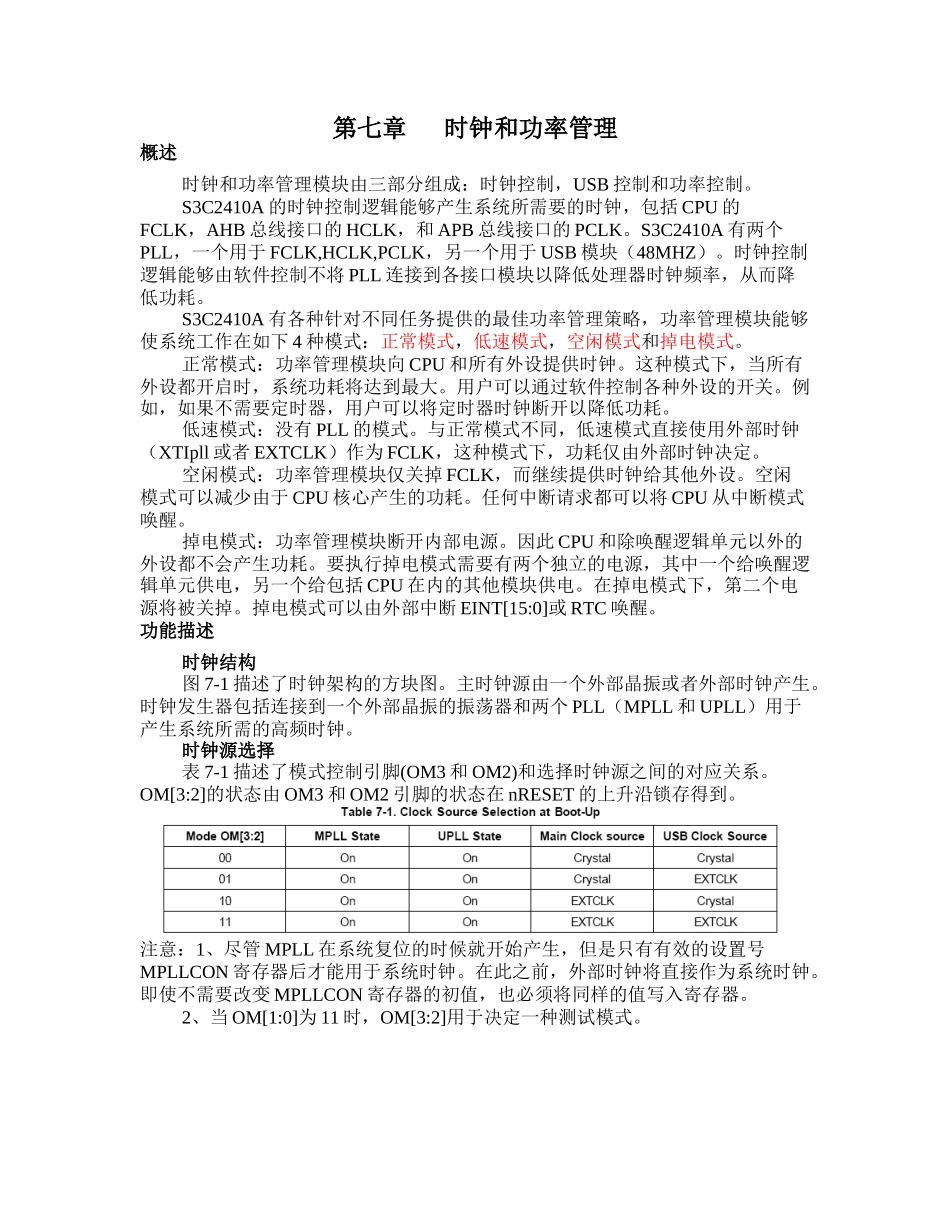

第七章时钟和功率管理概述时钟和功率管理模块由三部分组成:时钟控制,USB控制和功率控制。S3C2410A的时钟控制逻辑能够产生系统所需要的时钟,包括CPU的FCLK,AHB总线接口的HCLK,和APB总线接口的PCLK。S3C2410A有两个PLL,一个用于FCLK,HCLK,PCLK,另一个用于USB模块(48MHZ)。时钟控制逻辑能够由软件控制不将PLL连接到各接口模块以降低处理器时钟频率,从而降低功耗。S3C2410A有各种针对不同任务提供的最佳功率管理策略,功率管理模块能够使系统工作在如下4种模式:正常模式,低速模式,空闲模式和掉电模式。正常模式:功率管理模块向CPU和所有外设提供时钟。这种模式下,当所有外设都开启时,系统功耗将达到最大。用户可以通过软件控制各种外设的开关。例如,如果不需要定时器,用户可以将定时器时钟断开以降低功耗。低速模式:没有PLL的模式。与正常模式不同,低速模式直接使用外部时钟(XTIpll或者EXTCLK)作为FCLK,这种模式下,功耗仅由外部时钟决定。空闲模式:功率管理模块仅关掉FCLK,而继续提供时钟给其他外设。空闲模式可以减少由于CPU核心产生的功耗。任何中断请求都可以将CPU从中断模式唤醒。掉电模式:功率管理模块断开内部电源。因此CPU和除唤醒逻辑单元以外的外设都不会产生功耗。要执行掉电模式需要有两个独立的电源,其中一个给唤醒逻辑单元供电,另一个给包括CPU在内的其他模块供电。在掉电模式下,第二个电源将被关掉。掉电模式可以由外部中断EINT[15:0]或RTC唤醒。功能描述时钟结构图7-1描述了时钟架构的方块图。主时钟源由一个外部晶振或者外部时钟产生。时钟发生器包括连接到一个外部晶振的振荡器和两个PLL(MPLL和UPLL)用于产生系统所需的高频时钟。时钟源选择表7-1描述了模式控制引脚(OM3和OM2)和选择时钟源之间的对应关系。OM[3:2]的状态由OM3和OM2引脚的状态在nRESET的上升沿锁存得到。注意:1、尽管MPLL在系统复位的时候就开始产生,但是只有有效的设置号MPLLCON寄存器后才能用于系统时钟。在此之前,外部时钟将直接作为系统时钟。即使不需要改变MPLLCON寄存器的初值,也必须将同样的值写入寄存器。2、当OM[1:0]为11时,OM[3:2]用于决定一种测试模式。锁相环PLL位于时钟信号发生器的内部MPLL用于将输出信号和相关输入信号在相位和频率上同步起来。它包括如图7-2所示的一些基本模块:根据DC电压产生相应比例关系频率的压控振荡器(VCO),除数P(对输入频率Fin进行P分频),除数M(对VCO的输出频率进行M分频,分频后输入到相位频率探测器PFD),除数S(对MPLL输出频率Mpll进行分频),相差探测器,chargepump,loopfilter。MPLL的时钟输出Mpll和输入时钟Fin的关系如下式所示:UPLL和MPLL是完全一样的。下面的部分描述了MPLL的操作,包括相差探测器,chargepump,VCO,loopfilter。相位频率探测器PFD当PFD检测Fref和Fvco之间的相差时产生一个控制信号。Fref如图7-2所示。ChargepumpChargepump通过一个外部过滤器将PFD的控制信号转换成一个比例的电压关系来驱动VCO。LoopFilterPFD产生的控制信号可能在每一次Fref和Fvco比较的时候产生很大的偏差,为了防止VCO过载,一个低通滤波器将过滤掉控制信号的高频成分。滤波器就是常用的一节RC滤波器。压控振荡器VCOLoopfilter输出的电压驱动VCO,导致它的晶振频率根据平均电压线性地增加或降低。当Fref和Fvco的频率和相位都匹配时,PFD停止发送控制信号给chargepump,然后VCO频率保持不变,并且PLL保持固定于系统时钟。PLL和时钟发射器的通用条件PLL和时钟发生器通常使用如下条件注:1、值是可变的。2、FCLK必须大于X-tal或EXTCLK的3倍。时钟控制逻辑时钟控制逻辑决定哪个时钟源被使用,例如MPLL或者外部时钟。当PLL被配置到一个新的频率时,时钟控制逻辑将会停止FCLK直到PLL达到一个稳定的输出。时钟控制逻辑在上电复位和从掉电模式唤醒的情况下也是有效的。上电复位(XTIpll)图7-4显示了上电复位时的时钟行为。晶振在几毫秒内开始振荡。当OSC时钟稳定后,PLL根据默认PLL设置开始生效,但是通常这个时候是不稳定的,因此在软件重新配置PLLCON寄存器之前FCLK直接使用Fin而不是MPLL,即使用户不希望改变PLLCON的默认...