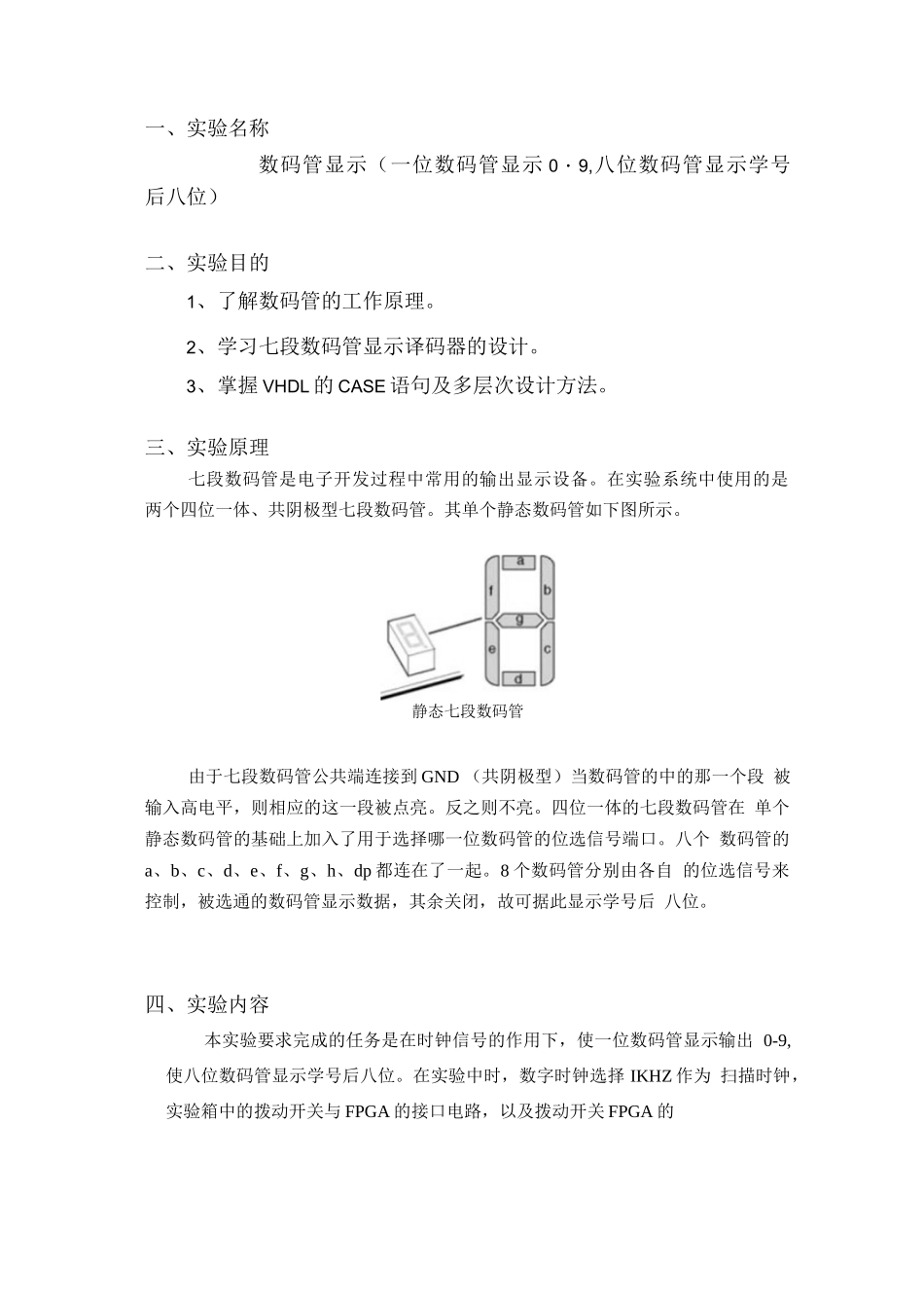

一、实验名称数码管显示(一位数码管显示0・9,八位数码管显示学号后八位)二、实验目的1、了解数码管的工作原理。2、学习七段数码管显示译码器的设计。3、掌握VHDL的CASE语句及多层次设计方法。三、实验原理七段数码管是电子开发过程中常用的输出显示设备。在实验系统中使用的是两个四位一体、共阴极型七段数码管。其单个静态数码管如下图所示。静态七段数码管由于七段数码管公共端连接到GND(共阴极型)当数码管的中的那一个段被输入高电平,则相应的这一段被点亮。反之则不亮。四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起。8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭,故可据此显示学号后八位。四、实验内容本实验要求完成的任务是在时钟信号的作用下,使一位数码管显示输出0-9,使八位数码管显示学号后八位。在实验中时,数字时钟选择IKHZ作为扫描时钟,实验箱中的拨动开关与FPGA的接口电路,以及拨动开关FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。以下两图分别是数码管显示模块的电路原理和其数码管的输入与FPGA的管脚连接表。74LS138信号名称对应FPGA管脚名说明7SEG-AF13七段码管A段输入信号7SEG-BF14七段码管B段输入信号7SEG-CF15七段码管C段输入信号7SEG-DE15七段码管D段输入信号7SEG-EF16七段码管E段输入信号7SEG-FF17七段码管F段输入信号7SEG-GE18七段码管G段输入信号7SEG-DPF18七段码管dp段输入信号7SEG-SEL0G18七段码管位选输入信号7SEG-SEL1G17七段码管位选输入信号7SEG-SEL2G16七段码管位选输入信号abcdefgdpaa■aOfflbOf∣7]b⅛⅜eGJeG⅞GdpdpdpdpGNDGNDGNDGNDabcdefgdpaaaa<∣g>fflbf∣7⅛f∣7]be小e∕d⅞e小e∕7⅞FPGA74HC245五、实验步骤1、打开QUARTUSIl软件,新建一个工程。2、建完工程之后,再新建一个VHDLFiIe,打开VHDL编辑器对话框。3、按照实验原理和自己的想法,在VHDL编辑窗口编写VHDL程序。其程序如下所示:(1)一位数码管显示0-9:1libraryieee;2useieee.std_logic_1164.all;3useieee.std_logic_arith.all;4useieee.std_logic__unsigned.all;5Hentityseg7is6Hport(elk:instd_logic;7rst:instd_logic;8dateout:outstd_logic_vector(6downto0));|9endseg7;10Harchitecturesadofseg7is11signaltmp:std_logic_vector(3downto0);12Hbegin13Sprocess(elk)14begin15Hifclk,eventandclk=,l,thentmp<=tjφ+l;16Bcasetmpis17whenπ0000π=>dateout<="1111110π;18whenn0001n=>dateout<="0110000n;19whenn0010,,≡>dateout<≡n1101101π;20when"0011π=>dateout<="1111001π;21when"0100n=>dateout<="0110011";22whenn0101,,=>dateout<≡"1011011";23whenn0110π=>dateout<="1011111";24wheπn0111n=>dateout<="1110000n;25when"1000n=>dateout<="lllllll";26whenn1001π=>dateout<="1111011";27whenothers=>dateout<≡nOOOOOOO";28endcase;29endif;30endprocess;31endsad;(2)八位数码管显示学号后八位:考拗三ITQ1LIBRARYIEEE;2USEIEEE.STD_LOGIC_1164-ALL;3USE工EEE.STD二LOG工UuNSIGNED.ALL;4BENTITYxh8IS5PORT(CLK:INSTD_LOGIC;6SG:OUTSTD_LOGIC__VECTOR(6DOWNTO0);7BT:OUTSTD二LOG工UVEeTOR(2DOWNTOO));8ENDxh8;9□ARCHITECTUREoneOFxh8IS10SIGNALCNT8:STD_LOGIC_VECTOR(2DOWNTOO);11SIGNALA:INTEGERRANGEOTO15;12BBEGIN13Hpl:PROCESS(Cnt8)14BEGIN15HCASEent8IS16WHEN"000”=>A<=4;17WHEN"001"=>A<=O;18WHEN"010"=>A<=8;19WHEN"011π->A<-3;20WHEN"100"≡>A<»O;21WHEN"101w=>A<=1;22WHEN"110"=>A<=2;23WHEN"111"≡>A<≡3;24WHENOTHERS->NULL;25ENDCASE;26ENDPROCESS;拿(%%治827Bp2:PROCESS(CLK)28BEGIN29CIFCLK,EVENTANDCLK=,1,THENCNT8<=CNT8+1;30ENDIF;31bt<=cnC8;32ENDPROCESSP2;33Hp3:PROCESS(A)34BEGIN35BCASEAIS36WHENO=>SG<=nOlllllln;WHEN1=>SG<=nOOOOllOn;37WHEN2=>SG<=∙'1011011∙,;WHEN3=>SG<=∙'1001111∙,;38WHEN4=>SG<=∙'1100110,';WHEN5=>SG<=∙'1101101∙,;39WHEN6=>SG<="IllllOln...