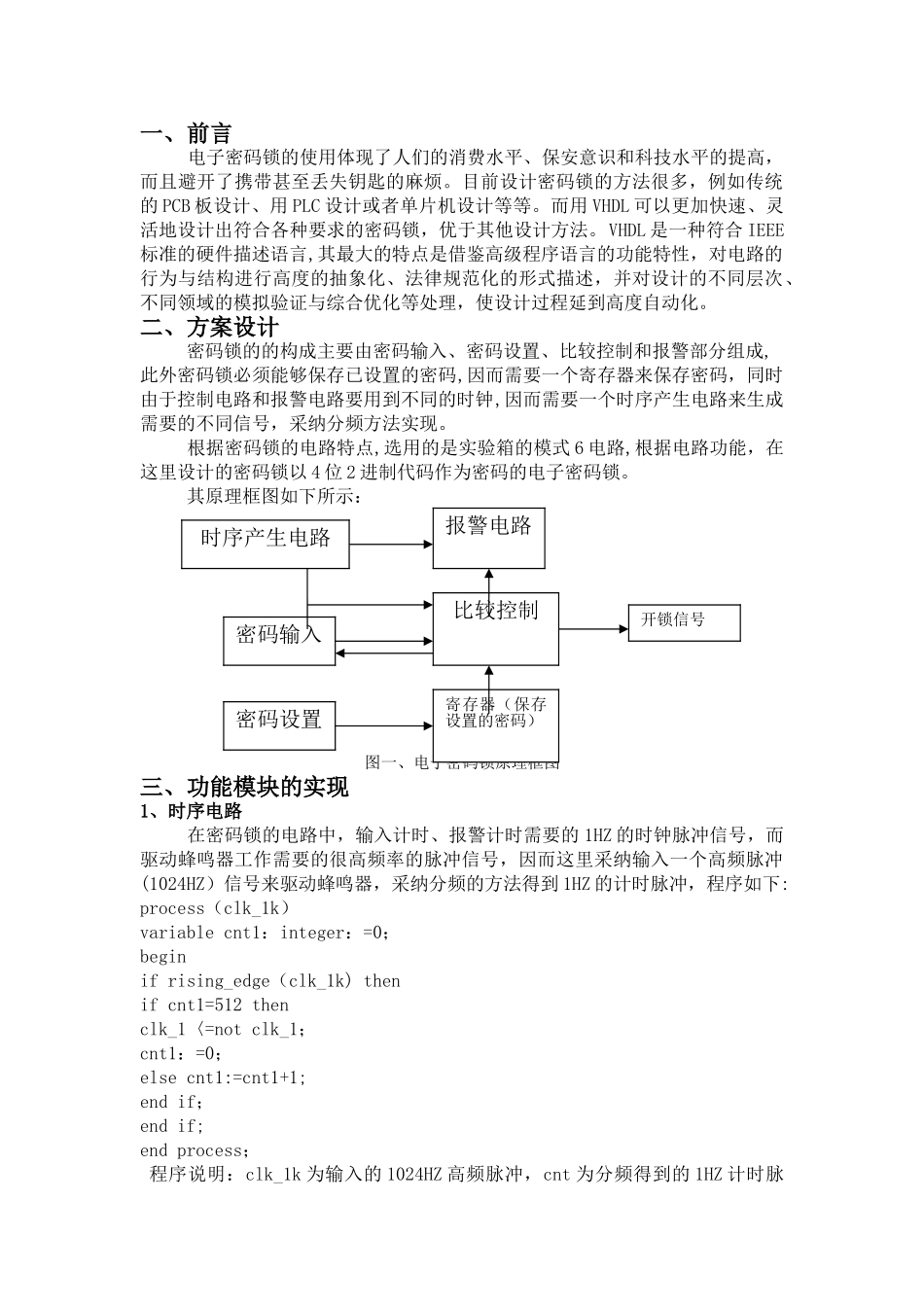

一、前言电子密码锁的使用体现了人们的消费水平、保安意识和科技水平的提高,而且避开了携带甚至丢失钥匙的麻烦。目前设计密码锁的方法很多,例如传统的 PCB 板设计、用 PLC 设计或者单片机设计等等。而用 VHDL 可以更加快速、灵活地设计出符合各种要求的密码锁,优于其他设计方法。VHDL 是一种符合 IEEE标准的硬件描述语言,其最大的特点是借鉴高级程序语言的功能特性,对电路的行为与结构进行高度的抽象化、法律规范化的形式描述,并对设计的不同层次、不同领域的模拟验证与综合优化等处理,使设计过程延到高度自动化。二、方案设计 密码锁的的构成主要由密码输入、密码设置、比较控制和报警部分组成,此外密码锁必须能够保存已设置的密码,因而需要一个寄存器来保存密码,同时由于控制电路和报警电路要用到不同的时钟,因而需要一个时序产生电路来生成需要的不同信号,采纳分频方法实现。 根据密码锁的电路特点,选用的是实验箱的模式 6 电路,根据电路功能,在这里设计的密码锁以 4 位 2 进制代码作为密码的电子密码锁。其原理框图如下所示:图一、电子密码锁原理框图三、功能模块的实现1、时序电路 在密码锁的电路中,输入计时、报警计时需要的 1HZ 的时钟脉冲信号,而驱动蜂鸣器工作需要的很高频率的脉冲信号,因而这里采纳输入一个高频脉冲(1024HZ)信号来驱动蜂鸣器,采纳分频的方法得到 1HZ 的计时脉冲,程序如下:process(clk_1k) variable cnt1:integer:=0;beginif rising_edge(clk_1k) thenif cnt1=512 thenclk_1〈=not clk_1;cnt1:=0;else cnt1:=cnt1+1;end if;end if;end process;程序说明:clk_1k 为输入的 1024HZ 高频脉冲,cnt 为分频得到的 1HZ 计时脉密码输入密码设置比较控制报警电路寄存器(保存设置的密码)开锁信号时序产生电路冲.2、密码设置为了安全性,密码锁必须能够重复的设定密码,在设定密码锁后,应该设置一个寄存器来存储设定的密码,程序如下:process(rst,password,enter_p) is beginif rst=’0’ thenif enter_p='1' thenram<=password;en1<=’1’;end if;end if;end process;程序说明:rst 低电平常所有的模块复位,只有密码设置模块工作;password 为设置密码时的输入端,ram 就是存储密码的寄存器;enter_p 为在这里为密码设置使能端,高电平有效。 密码设置的仿真波形如下图,由图中可以清楚地看到在 enter_p 高电平常寄存器 ram 中得到了输入的...