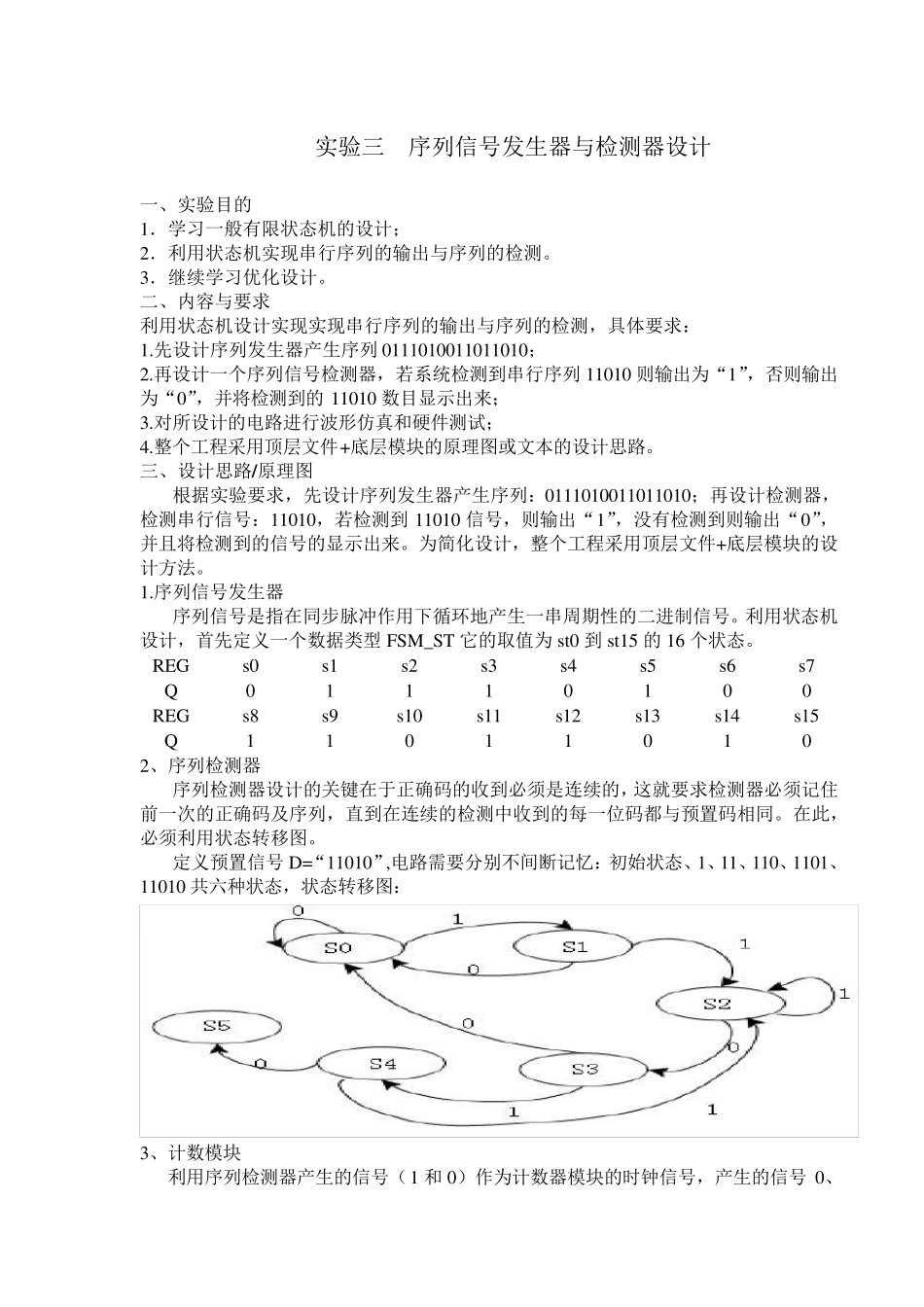

实验三 序列信号发生器与检测器设计 一、实验目的 1.学习一般有限状态机的设计; 2.利用状态机实现串行序列的输出与序列的检测。 3.继续学习优化设计。 二、内容与要求 利用状态机设计实现实现串行序列的输出与序列的检测,具体要求: 1.先设计序列发生器产生序列0111010011011010; 2.再设计一个序列信号检测器,若系统检测到串行序列11010 则输出为“1”,否则输出为“0”,并将检测到的11010 数目显示出来; 3.对所设计的电路进行波形仿真和硬件测试; 4.整个工程采用顶层文件+底层模块的原理图或文本的设计思路。 三、设计思路/原理图 根据实验要求,先设计序列发生器产生序列:0111010011011010;再设计检测器,检测串行信号:11010,若检测到11010 信号,则输出“1”,没有检测到则输出“0”,并且将检测到的信号的显示出来。为简化设计,整个工程采用顶层文件+底层模块的设计方法。 1.序列信号发生器 序列信号是指在同步脉冲作用下循环地产生一串周期性的二进制信号。利用状态机设计,首先定义一个数据类型 FSM_ST 它的取值为st0 到st15 的16 个状态。 REG s0 s1 s2 s3 s4 s5 s6 s7 Q 0 1 1 1 0 1 0 0 REG s8 s9 s10 s11 s12 s13 s14 s15 Q 1 1 0 1 1 0 1 0 2、序列检测器 序列检测器设计的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及序列,直到在连续的检测中收到的每一位码都与预置码相同。在此,必须利用状态转移图。 定义预置信号D=“11010”,电路需要分别不间断记忆:初始状态、1、11、110、1101、11010 共六种状态,状态转移图: 3、计数模块 利用序列检测器产生的信号(1 和 0)作为计数器模块的时钟信号,产生的信号0、 1 变化,形成类似的CLK 信号,实现计数模块计数。计数模块设计可采用前面的实验二设计。 4.顶层设计 为简化设计,顶层设计采用原理图输入法设计,直接将模块进行连接。 四、实验程序(陈杰独立编写) 序列信号发生器: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY C_OUT IS PORT (CLK,RST :IN STD_LOGIC; CO :OUT STD_LOGIC ); END C_OUT; ARCHITECTURE behav OF C_OUT IS TYPE FSM_ST IS (s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,s14,s15); SIGNAL REG:FSM_ST; SIGNAL Q:STD_LOGIC; BEGIN PROCESS(CLK,RST) BEGIN IF RST ='1' THEN REG<=...