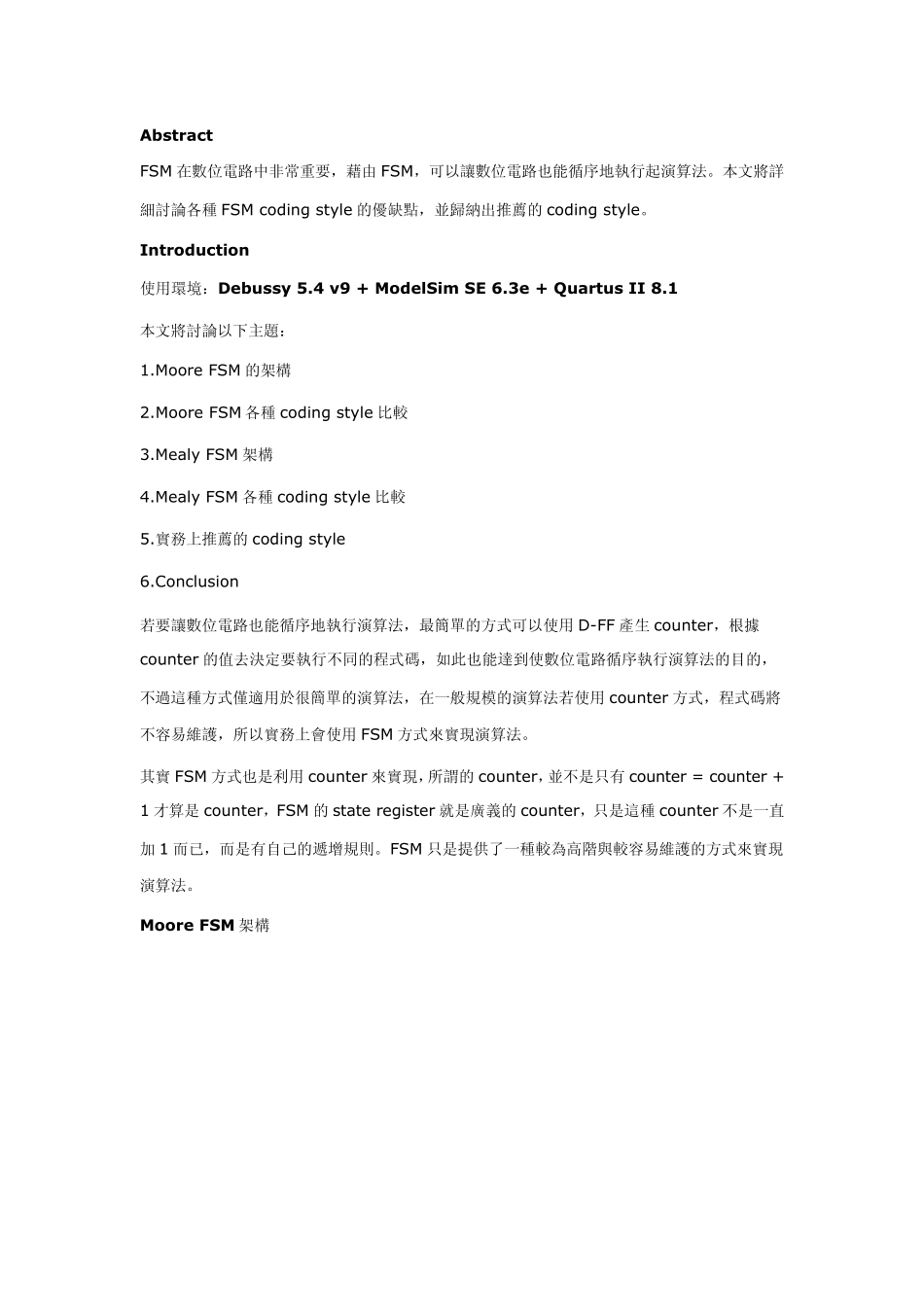

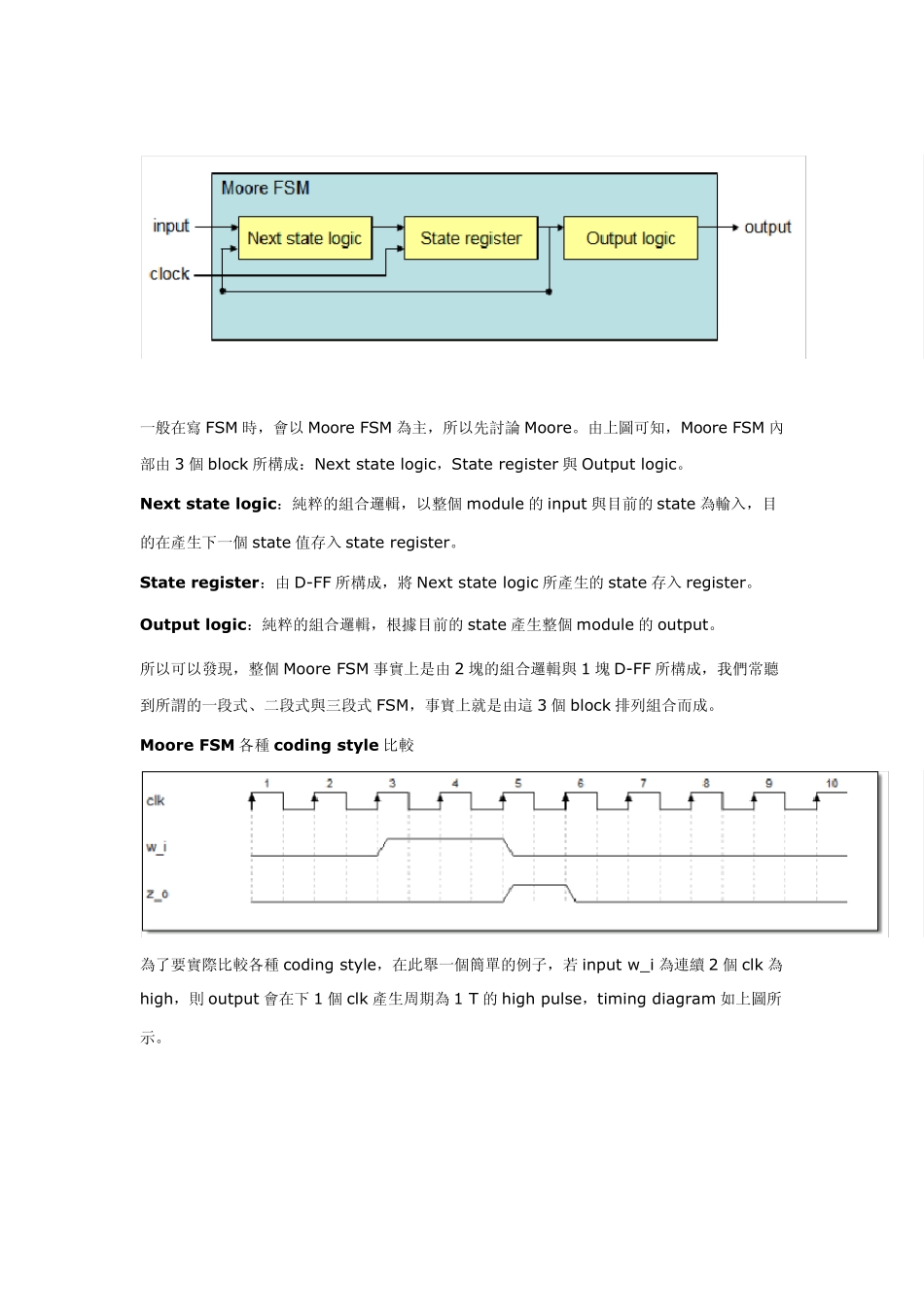

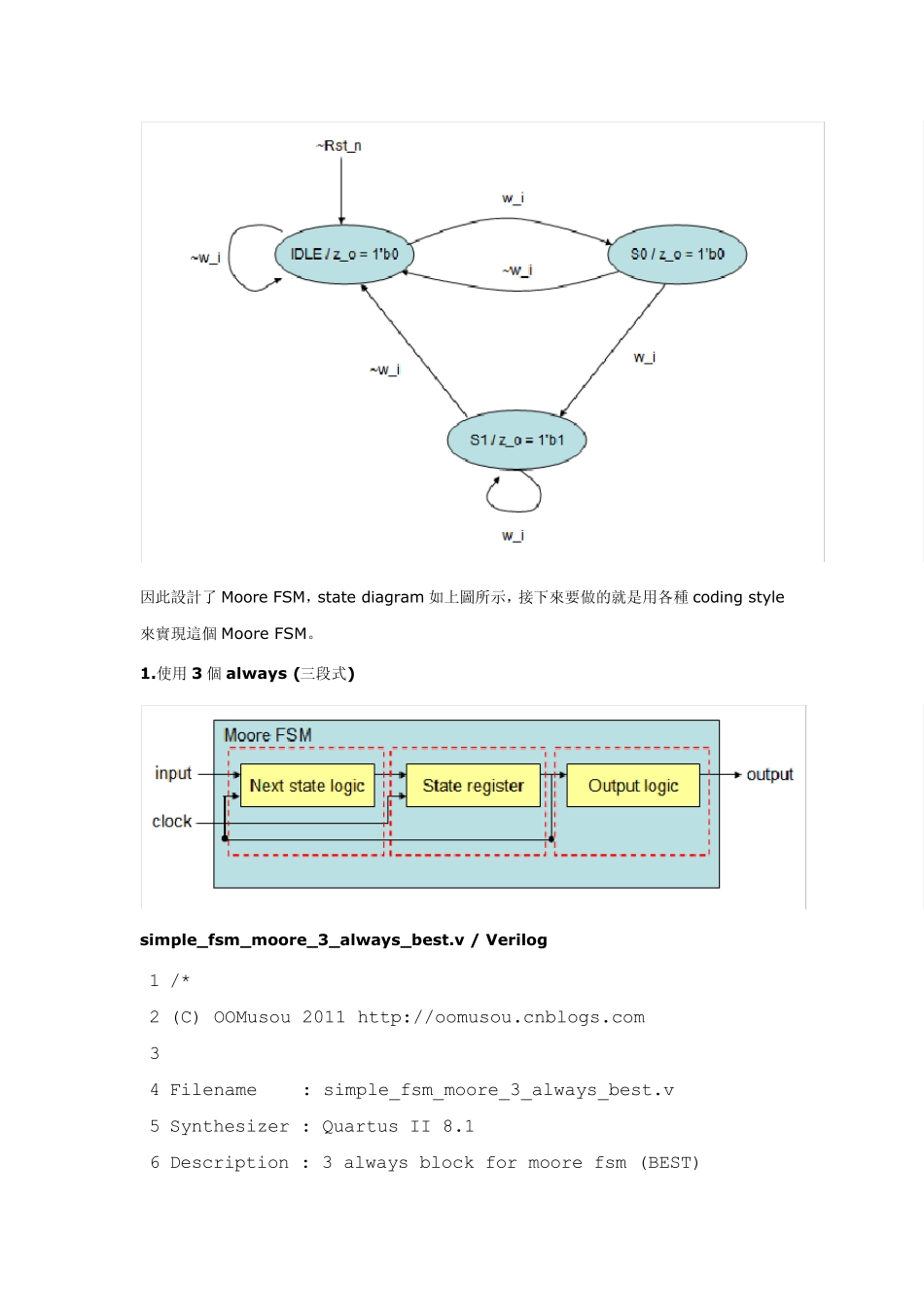

Abstract FSM 在數位電路中非常重要,藉由FSM,可以讓數位電路也能循序地執行起演算法。本文將詳細討論各種 FSM coding style 的優缺點,並歸納出推薦的 coding style。 Introduction 使用環境:Debussy 5.4 v9 + ModelSim SE 6.3e + Quartus II 8.1 本文將討論以下主題: 1.Moore FSM 的架構 2.Moore FSM 各種 coding style 比較 3.Mealy FSM 架構 4.Mealy FSM 各種 coding style 比較 5.實務上推薦的 coding style 6.Conclusion 若要讓數位電路也能循序地執行演算法,最簡單的方式可以使用 D-FF 產生 counter,根據counter 的值去決定要執行不同的程式碼,如此也能達到使數位電路循序執行演算法的目的,不過這種方式僅適用於很簡單的演算法,在一般規模的演算法若使用 counter 方式,程式碼將不容易維護,所以實務上會使用 FSM 方式來實現演算法。 其實 FSM 方式也是利用 counter 來實現,所謂的 counter,並不是只有 counter = counter + 1 才算是 counter,FSM 的 state register 就是廣義的 counter,只是這種 counter 不是一直加 1 而已,而是有自己的遞增規則。FSM 只是提供了一種較為高階與較容易維護的方式來實現演算法。 Moore FSM 架構 一般在寫FSM 時,會以Moore FSM 為主,所以先討論Moore。由上圖可知,Moore FSM 內部由3 個block 所構成:Next state logic,State register 與Output logic。 Next state logic:純粹的組合邏輯,以整個module 的input 與目前的state 為輸入,目的在產生下一個state 值存入state register。 State register:由D-FF 所構成,將Next state logic 所產生的state 存入register。 Output logic:純粹的組合邏輯,根據目前的state 產生整個module 的output。 所以可以發現,整個Moore FSM 事實上是由2 塊的組合邏輯與1 塊D-FF 所構成,我們常聽到所謂的一段式、二段式與三段式FSM,事實上就是由這 3 個block 排列組合而成。 Moore FSM 各種 coding style 比較 為了要實際比較各種 coding style,在此舉一個簡單的例子,若 input w_i 為連續 2 個clk 為high,則 output 會在下1 個clk 產生周期為1 T 的high pulse,timing diagram 如上圖所示。 因此設計了Moore FSM,state diagram 如上圖所示,接下來要做的就是用各種coding sty le來實現這個Mo...

VIP

VIP VIP

VIP VIP

VIP VIP

VIP VIP

VIP VIP

VIP VIP

VIP VIP

VIP VIP

VIP VIP

VIP