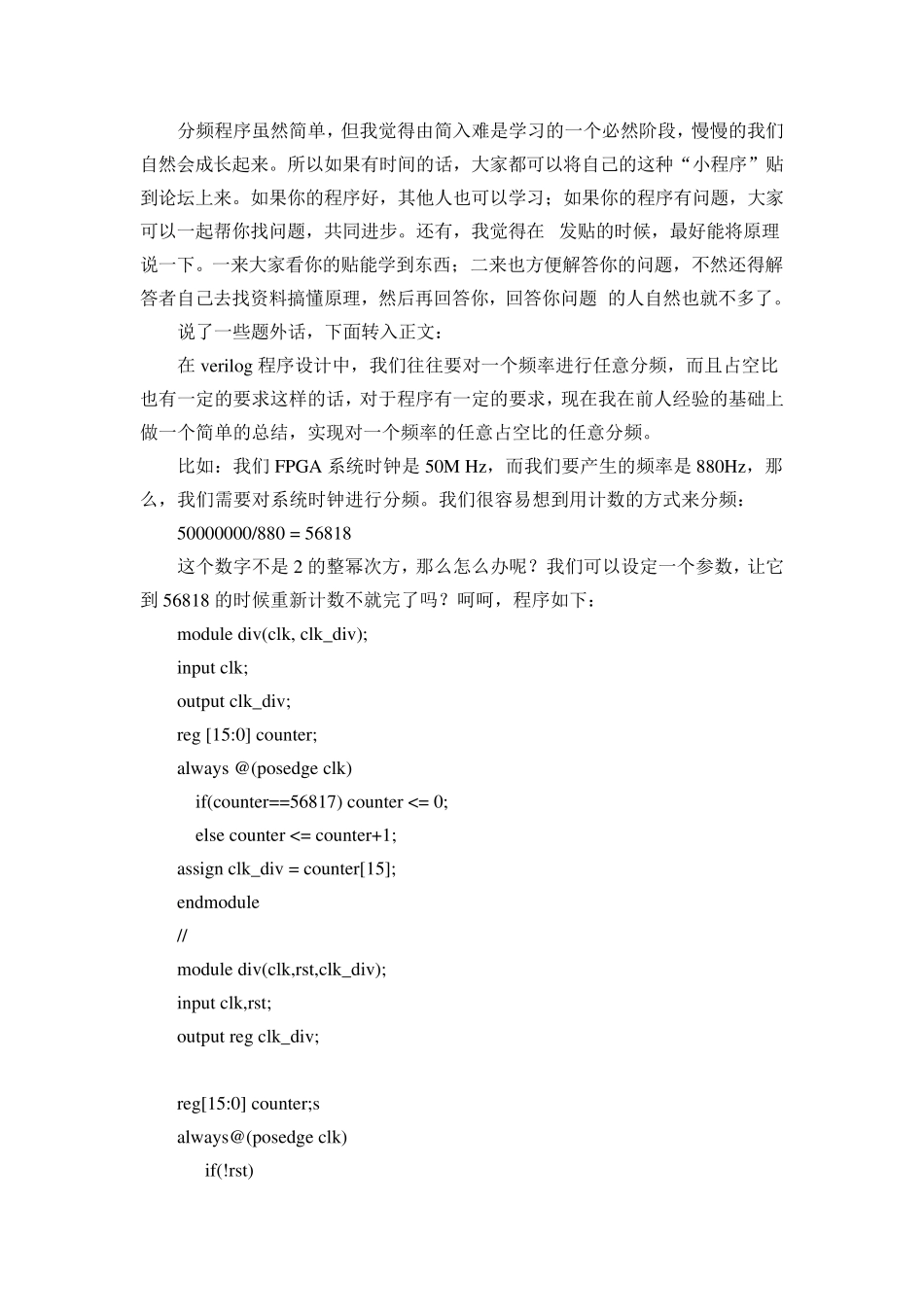

分频程序虽然简单,但我觉得由简入难是学习的一个必然阶段,慢慢的我们自然会成长起来。所以如果有时间的话,大家都可以将自己的这种“小程序”贴到论坛上来。如果你的程序好,其他人也可以学习;如果你的程序有问题,大家可以一起帮你找问题,共同进步。还有,我觉得在 发贴的时候,最好能将原理说一下。一来大家看你的贴能学到东西;二来也方便解答你的问题,不然还得解答者自己去找资料搞懂原理,然后再回答你,回答你问题 的人自然也就不多了。 说了一些题外话,下面转入正文: 在 verilog 程序设计中,我们往往要对一个频率进行任意分频,而且占空比也有一定的要求这样的话,对于程序有一定的要求,现在我在前人经验的基础上做一个简单的总结,实现对一个频率的任意占空比的任意分频。 比如:我们FPGA 系统时钟是50M Hz,而我们要产生的频率是880Hz,那么,我们需要对系统时钟进行分频。我们很容易想到用计数的方式来分频: 50000000/880 = 56818 这个数字不是2 的整幂次方,那么怎么办 呢 ? 我们可以设定一个参 数,让 它到 56818 的时候重 新 计数不就完 了吗 ? 呵 呵 ,程序如下: module div(clk, clk_div); input clk; output clk_div; reg [15:0] counter; always @(posedge clk) if(counter==56817) counter <= 0; else counter <= counter+1; assign clk_div = counter[15]; endmodule // module div(clk,rst,clk_div); input clk,rst; output reg clk_div; reg[15:0] counter;s always@(posedge clk) if(!rst) begin counter<=0; clk_div<=0; end else if (counter==56817) begin counter<=0; clk_div<~clk_div; end else counter<=counter+1; endmodule 下面我们来算一下它的占空比:我们清楚地知道,这个输出波形在counter为0 到32767 的时候为低,在32767 到56817 的时候为高,占空比为40%多一些,如果我们需要占空比为50%,那么怎么办呢?不用急,慢慢来。 我们再设定一个参数,使它为56817 的一半,使达到它的时候波形翻转,那不就完了吗?呵呵,再看看: module div(clk, clk_div); input clk; output clk_div; reg [14:0] counter; always @(posedge clk) if(counter==28408) counter <= 0; else counter <= counter+1; reg clk_div; always @(posedge clk) if(counter==28408) clk_div <= ~clk_d...